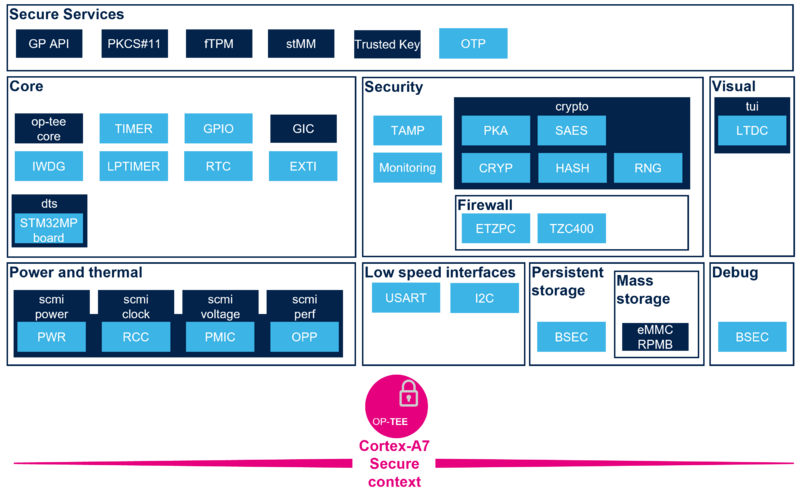

This section gives an overview of OP-TEE core drivers (UPPERCASE in the figure) implemented for the STM32MP13 support, with their respective software frameworks (lowercase in the figure).

It is running in the Cortex-A7 secure context (EL1S execution level).

Due to the Armv-7a architecture, it also runs a dedicated secure monitor which is running in Cortex-A7 EL3 and which is providing Cortex-A7 cluster low power functionalities via PSCI interface.

OP-TEE is in charge of:

- System resources management

- Internal and external regulators

- Clock tree (PLLs and Root clocks)

- System peripheral clock gating

- Oscillators calibration

- Firewall configuration and dynamic management

- OTP access

- Wakeup pins

- Secure services

- Cryptography via Global Platform (GP) API

- PKCS#11

- Trusted UI

- StMM for secure UEFI

- fTPM (firmware TPM) for TPM2 services

- OTP for provisioning

- SecCopro for secure coprocessor management

As mentioned in the STM32 MPU OP-TEE overview, the different features can be independently activated according to the customers needs.

The following figure provides an overview of the STM32MP13x lines ![]() OP-TEE.

OP-TEE.

The components are grouped by functional domains.

Each OP-TEE framework is further described in the OP-TEE category articles.

Each STM32 MPU peripheral is introduced in the peripherals overview articles.

Both sections are reusing the same functional domain split.

The color code, explained in the legend, allows to see the code origin for each component.