1. Article purpose[edit | edit source]

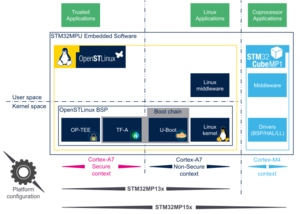

This article introduces STM32CubeMP15 Package / STM32CubeMP1 Package (a.k.a., STM32CubeMP15 / STM32CubeMP1) architecture based on the Arm® Cortex®-M4 processor, acting as coprocessor of the Arm® Cortex®-A7.

- Refer to STM32CubeMP15 Package - Getting started article to get started.

2. Architecture overview[edit | edit source]

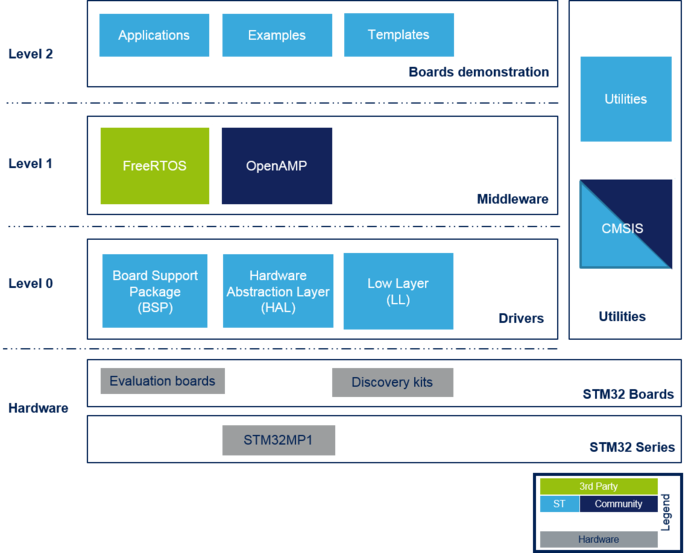

The STM32CubeMP15 Package gathers together, in a single package, all the generic embedded software components required to develop applications on top of Arm® Cortex®-M4 microprocessors.

On top of the hardware, the STM32CubeMP15 Package solution is built around three levels of software components (Level 0 for Drivers, level 1 for Middleware, Level 2 for Boards demonstrations), that interact easily with each other. It also includes 2 common components CMSIS and Utilities which interact with all three levels.

Notes:

|

3. Level 0 (Drivers)[edit | edit source]

This level is divided into three software components:

- Hardware Abstraction Layer (HAL)

- Low Layer (LL)

- Board Support Package (BSP)

3.1. HAL drivers[edit | edit source]

The HAL drivers provide the low level drivers and the hardware interfacing methods to interact with the upper layers (application, libraries and stacks). They provide generic, multi instance and function-oriented APIs which simplify user application implementation by providing ready-to-use processes.

As example, for the communication peripherals (I2C, UART…), they include APIs allowing to initialize and configure the peripheral, to manage data transfer based on polling, interrupt or DMA process, and to handle communication errors that may raise during communication.

Note:

|

3.1.1. HAL drivers overview[edit | edit source]

The HAL APIs layer is composed of native and extended APIs set. It is directly built around a generic architecture and allows the build-upon layers, like the middleware layer, to implement its functions without in-depth knowledge about the used STM32 device. This improves the library code reusability and guarantees an easy portability on other devices and STM32 families

Contrary to the low layer drivers (see Low Layer section), the HAL ones are functionality-oriented and not internal peripheral-oriented.

Example: for the Timer peripheral, the APIs could be split into several categories following the functions offered by the internal peripherals (Basic timer, capture, PWM …etc.).

The HAL drivers are a set of common APIs with a high compliancy level with most of the clients available on the market (stacks) called native APIs and embed also some extended functionalities for special services or a combination of several features offered by the STM32 peripherals

The HAL drivers APIs are split in two categories:

- Generic APIs which provide common and generic functions to all the STM32 series

- Extension APIs which provide specific customized functions for a specific family or a specific part number

3.1.2. List of HAL drivers[edit | edit source]

The list of HAL drivers available for STM32MP1xx family is accessible in HAL drivers.

3.2. LL drivers[edit | edit source]

The Low Layer (LL) drivers offer a fast light-weight expert-oriented layer which is closer to the hardware than the HAL. The LL APIs are available only for a set of peripherals.

3.2.1. LL drivers overview[edit | edit source]

The Low Layer (LL) drivers are part of the STM32CubeMPU firmware HAL that provides basic set of optimized and one-shot services. The Low layer drivers, contrary to the HAL ones are not fully portable across the STM32 families; the availability of some functions depends on the physical availability of the relative features on the product.

The Low Layer (LL) drivers are designed to offer the following features:

- New set of inline functions for direct and atomic register access,

- One-shot operations that can be used by the HAL drivers or from application level,

- Fully independent from HAL and can be used in standalone usage (without HAL drivers),

- Full feature coverage of all the supported peripherals.

3.2.2. List of LL drivers[edit | edit source]

The list of LL drivers available for STM32MP1xx family is accessible in LL drivers.

3.3. BSP drivers[edit | edit source]

The BSP drivers are firmware components based on the HAL drivers and provide a set of APIs relative to the hardware components in the evaluation boards coming with the STM32Cube Package. All examples and applications given with the STM32Cube are based on these BSP drivers.

3.3.1. BSP drivers overview[edit | edit source]

The BSP architecture proposes a new model that prevents some standard library weaknesses and provides more features:

- Portable external resources code (components): the external components could be used by all STM32 families,

- Multiple use of hardware resources without duplicated initialization: example: I2C Physical Layer could be used for several EVAL Drivers ,

- Intuitive functionalities based on high level use case,

- Portable BSP drivers for different external devices.

3.3.2. List of BSP drivers[edit | edit source]

The BSP drivers offer a set of APIs relative to the hardware components available in the hardware boards (LEDs, Buttons and COM port). Refer to BSP_drivers

4. Level 1 (Middlewares)[edit | edit source]

Middleware components are a set of libraries providing a set of services. STM32CubeMP15 Package offers 2 main components :

Each middleware component is mainly composed of:

- Library core: this is the core of a component; it manages the main library state machine and the data flow between the several modules,

- Interface layer: the interface layer is generally used to link the component core with the lower layers like the HAL and the BSP drivers.

4.1. OpenAMP[edit | edit source]

OpenAMP [1] is a library implementing the Remote Processor Service framework (RPMsg) which is a messaging mechanism to communicate with a remote processor.

- Load and control Arm® Cortex®-M4 firmware

- Inter processor communication

Note:

|

4.2. FreeRTOS[edit | edit source]

FreeRTOS [2] is a Free Real Time Operating System (RTOS). The FreeRTOS offers preemptive real-time performance with optimized context switch and interrupt times, enabling fast, highly predictable response times.

It includes the following main features :

- Small memory fingerprint

- High portability

- Multithread management

- Pre-emptive scheduling

- Fast interrupt response

- Extensive inter-process communication

- Synchronization facilities

- Tickless operation during low-power mode

- Open source standard

- CMSIS compatibility layer

5. Level 2 (Boards demonstrations)[edit | edit source]

The Boards demonstrations level is composed of a single layer which provides all examples and applications. It includes also all STM32CubeIDE projects for each supported board as well as templates source files.

There are 4 kinds of projects demonstrating different usages of software APIs from level 0 (Drivers) and level 1 (Middleware):

- Examples projects showing how to use HAL APIs and Low Layer drivers if any (Level 0) with very basic usage of BSP layer (buttons and LEDs in general)

- Applications projects showing how to use the middleware components (Level 1) and how to integrate them with the hardware and BSP/HAL layers (Level 0). These applications could be hybrid and use several other middleware components.

- Demonstrations projects showing how to integrate and run a maximum number of peripherals and middleware stacks to showcase the product features and performance

- Templates projects is a really basic user application including STM32CubeIDE projects files, which could be used to start a custom project

Notes:

|

6. Utilities[edit | edit source]

The Utilities is a set of common utilities and services offered by STM32CubeMP15 Package and is composed of different components :

└── Utilities

└── ResourcesManager Services for coprocessing in multi-core devices. Refer to Resource manager for coprocessing

7. CMSIS[edit | edit source]

The Cortex Microcontroller Software Interface Standard (CMSIS) is a vendor-independent hardware abstraction layer for the Arm® Cortex®-M4 processor series.

- Refer to CMSIS[3] to get more information on CMSIS component.

The CMSIS component also provides specific common resources for device support. It enables consistent and simple software interfaces to the processor and the peripherals, simplifying software re-use, reducing the learning curve for microcontroller developers, and reducing the time to market for new devices

This vendor part is called CMSIS Device and it provides interrupt list, peripherals registers description and associated defines for all registers bit fields.

- CMSIS structure overview:

├── CMSIS │ ├── Core │ │ ├── Include │ │ └── Template │ ├── Core_A │ │ ├── Include │ │ └── Template │ ├── Device CMSIS Device │ │ └── ST │ │ │ └── STM32MP1xx Common resources for STM32MP1xx family │ ├── docs │ │ ├── Core │ │ ├── Core_A │ │ ├── DAP │ │ ├── Driver │ │ ├── DSP │ │ ├── General │ │ ├── index.html │ │ ├── Pack │ │ ├── RTOS │ │ ├── RTOS2 │ │ ├── SVD │ │ └── Zone │ ├── DSP │ │ ├── Examples │ │ ├── Include │ │ └── Source │ ├── Include │ │ ├── cmsis_armcc.h │ │ ├── cmsis_armclang.h │ │ ├── cmsis_compiler.h │ │ ├── cmsis_gcc.h │ │ ├── cmsis_iccarm.h │ │ ├── cmsis_version.h │ │ ├── core_armv8mbl.h │ │ ├── core_armv8mml.h │ │ ├── core_cm0.h │ │ ├── core_cm0plus.h │ │ ├── core_cm23.h │ │ ├── core_cm33.h │ │ ├── core_cm3.h │ │ ├── core_cm4.h │ │ ├── core_cm7.h │ │ ├── core_sc000.h │ │ ├── core_sc300.h │ │ ├── mpu_armv7.h │ │ ├── mpu_armv8.h │ │ └── tz_context.h │ ├── LICENSE.txt │ ├── README.md │ ├── RTOS │ │ └── Template │ └── RTOS2 │ ├── Include │ ├── Source │ └── Template

- CMSIS Device structure :

├── CMSIS │ ├── Device CMSIS Device │ │ └── ST │ │ │ └── |STM32MP1xx Common resources for STM32MP1xx family │ │ │ │ ├── Include Device resources definition │ │ │ │ │ ├── stm32mp151axx_cm4.h │ │ │ │ │ ├── stm32mp151axx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp151cxx_cm4.h │ │ │ │ │ ├── stm32mp151cxx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp151dxx_cm4.h --> for 800MHz │ │ │ │ │ ├── stm32mp151dxx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp151fxx_cm4.h --> for 800MHz │ │ │ │ │ ├── stm32mp151fxx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp153axx_cm4.h │ │ │ │ │ ├── stm32mp153axx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp153cxx_cm4.h │ │ │ │ │ ├── stm32mp153cxx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp153dxx_cm4.h --> for 800MHz │ │ │ │ │ ├── stm32mp153dxx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp153fxx_cm4.h --> for 800MHz │ │ │ │ │ ├── stm32mp153fxx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp157axx_cm4.h │ │ │ │ │ ├── stm32mp157axx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp157cxx_cm4.h │ │ │ │ │ ├── stm32mp157cxx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp157dxx_cm4.h --> for 800MHz │ │ │ │ │ ├── stm32mp157dxx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp157fxx_cm4.h --> for 800MHz │ │ │ │ │ ├── stm32mp157fxx_ca7.h --> Added "as example" │ │ │ │ │ ├── stm32mp1xx.h │ │ │ │ │ └── system_stm32mp1xx.h │ │ │ │ │── Release_Notes.html │ │ │ │ └── Source │ │ │ │ │ └── Templates │ │ │ │ │ │ ├── arm linker files and startup files (memory mapping) │ │ │ │ │ │ │ ├── linker │ │ │ │ │ │ │ │ └── stm32mp15xx_m4.sct │ │ │ │ │ │ │ ├── startup_stm32mp15xx.s │ │ │ │ │ │ ├── gcc linker files and startup files (memory mapping) │ │ │ │ │ │ │ ├── linker │ │ │ │ │ │ │ │ └── stm32mp15xx_m4.ld │ │ │ │ │ │ │ ├── startup_stm32mp15xx.s │ │ │ │ │ │ │ ├── startup_stm32mp151a_cm4.s --> Added to fit with the resources available │ │ │ │ │ │ │ ├── startup_stm32mp151c_cm4.s --> Added to fit with the resources available │ │ │ │ │ │ │ ├── startup_stm32mp153a_cm4.s --> Added to fit with the resources available │ │ │ │ │ │ │ ├── startup_stm32mp153c_cm4.s --> Added to fit with the resources available │ │ │ │ │ │ │ ├── startup_stm32mp157a_cm4.s --> Added to fit with the resources available │ │ │ │ │ │ │ ├── startup_stm32mp157c_cm4.s --> Added to fit with the resources available │ │ │ │ │ │ ├── iar linker files and startup files (memory mapping) │ │ │ │ │ │ │ ├── linker │ │ │ │ │ │ │ │ └── stm32mp15xx_sram.icf │ │ │ │ │ │ │ ├── startup_stm32mp15xx.s │ │ │ │ │ │ └── system_stm32mp1xx.c

Notes:

|

8. STM32CubeMP15 Package versus legacy STM32Cube MCU Package[edit | edit source]

STM32 MPU devices introduce light differences with STM32 MCU. Find hereafter a short description of the main differences between STM32CubeMP15 Package and STM32Cube MCU Package:

- The middleware and BSP components offer is smaller in STM32CubeMP15 Package as we can take advantage of a rich OS like Linux® running on Arm® Cortex®-A7 core for networking, USB, visual and audio services

Notes:

|

- There is no Flash HAL driver as there is no volatile embedded FLASH dedicated to Arm® Cortex®-M4 in MPU devices

- Specific pieces of software have been added to handle multi-core operations:

- OpenAMP middleware for Intercommunication processor between Arm® Cortex®-A7 and Arm® Cortex®-M4 (RPMsg protocol implementation)

- Resource Manager library for system resource management

- Virtual UART driver (specific usage when Linux is used on Arm® Cortex®-A7)

- Linux script to load STM32CubeMPU firmware running on Arm® Cortex®-M4 core (specific usage when Linux is used on Arm® Cortex®-A7)

Note:

|

9. References[edit | edit source]