1. Article purpose[edit | edit source]

The purpose of this article is to:

- Briefly introduce the STGEN peripheral and its main features.

- Indicate the peripheral instance assignments at boot time and runtime (including whether instances can be allocated to secure contexts).

- List the software frameworks and drivers managing the peripheral.

- Explain how to configure the peripheral.

2. Peripheral overview[edit | edit source]

The STGEN peripheral provides the reference clock used by the Arm® Cortex®-Axxx generic timer [1]for its counters, including the system tick generation.

It is clocked by either the HSI (High Speed Internal) oscillator or the HSE (High Speed External) oscillator. During the boot phase, STGEN is clocked by HSI until HSE is set up. This should be done at an early stage. Caution is needed when switching from one source to another, as the STGEN counter must be updated according to the new frequency. Otherwise, the time reference will be incorrect.

The STGEN is a single-instance peripheral that can be accessed via the following two register sets:

- STGENC for control: the secure port.

- STGENR for read-only access: the nonsecure port.

Refer to the STM32 MPU reference manuals for the complete list of features, and to the software frameworks and drivers, introduced in chapter 4 below, to see which features are implemented.

On Arm 64-bit platforms, the update of the Arm CPU counter register can only be done by the highest exception level, which is TF-A BL31 on the STM32MP2 series.

3. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s).

3.1. Boot time assignment[edit | edit source]

3.1.1. On STM32MP1 series[edit | edit source]

The STGEN is first initialized by the ROM code, then updated by the FSBL (see Boot chain overview) once the HSE clock is set up.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 nonsecure (U-Boot) | |||

| Core | STGEN | STGEN | ✓ | ✓ | ||

3.1.2. On STM32MP2 series[edit | edit source]

3.1.2.1. For A35-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) | |||

| Core | STGEN | STGEN | ✓ | ☑ | Read-only (STGENR) |

|

3.1.2.2. For M33-TD flavor  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32 MPU reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 nonsecure (U-Boot) |

Cortex-M33 secure (MCUboot) | |||

| Core | STGEN | STGEN | ✓ | ☑ | Read-only (STGENR) |

||

3.2. Runtime assignment[edit | edit source]

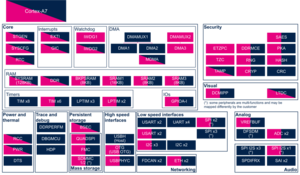

3.2.1. On STM32MP13x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP13 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) | |||

| Core | STGEN | STGEN | ✓ | ||

3.2.2. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possiblities might be described in STM32MP15 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Core | STGEN | STGEN | ✓ | |||

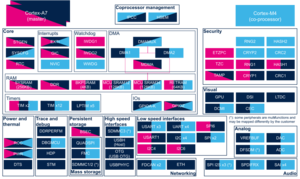

3.2.3. On STM32MP21x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP21 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Core | STGEN | STGEN | ☑OP-TEE ☑TF-A BL31 |

Read-only (STGENR) |

|||

3.2.4. On STM32MP23x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP23 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | ||||

|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) | |||

| Core | STGEN | STGEN | ☑OP-TEE ☑TF-A BL31 |

Read-only (STGENR) |

|||

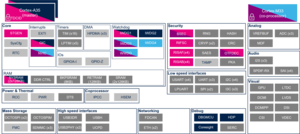

3.2.5. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

The tables below are applicable to any TD flavor (A35-TD or M33-TD) ![]() .

.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by the OpenSTLinux BSP:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in OpenSTLinux BSP.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the OpenSTLinux BSP.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

Refer to How to assign an internal peripheral to an execution context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP25 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 nonsecure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 nonsecure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Core | STGEN | STGEN | ☑OP-TEE ☑TF-A BL31 |

Read-only (STGENR) |

||||

4. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the STGEN peripheral for the embedded software components listed in the above tables.

Linux®/U-Boot use the Arm® Cortex®-Axxx generic timer that gets its counter from the STGEN, but this is transparent at runtime. Therefore, there is no noticeable framework or driver for these components.

4.1. STM32MP1 series[edit | edit source]

In OP-TEE, the STGEN's counter value is saved/restored during low-power sequences to keep platform time coherence. The STGEN configuration is done by TF-A. The frequency of the counter is restored in TF-A as well.

4.2. STM32MP2 series[edit | edit source]

The STGEN configuration/restore is done by OP-TEE and the Arm counter frequency is set by TF-A BL31 upon receiving a specific SMC call from OP-TEE.

4.3. Sources[edit | edit source]

- TF-A:

- drivers/st/clk/stm32mp_clkfunc.c STGEN configuration and frequency restoration

- plat/st/stm32mp2/services/stgen_svc.c STGEN service in BL31 for STM32MP2 series

- OP-TEE:

- core/arch/arm/plat-stm32mp1/pm/context.c : Save STGEN value in pm context during low power

- core/drivers/counter/stm32_stgen.c : STGEN driver for STM32MP2 series

5. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and completed manually, if necessary).

This tool can also be used to configure the peripheral:

- Partial device tree (pin control and clock tree) generation for the OpenSTLinux software components.

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context to which the peripheral is assigned.

6. References[edit | edit source]

- ↑ The ARM Generic Timer: the timer framework for A-profile

https://developer.arm.com/documentation/102379/0104/What-is-the-Generic-Timer-