Registered User mNo edit summary |

Registered User mNo edit summary |

||

| Line 3: | Line 3: | ||

|MPUs checklist=STM32MP13x, STM32MP15x | |MPUs checklist=STM32MP13x, STM32MP15x | ||

}}</noinclude> | }}</noinclude> | ||

{{ReviewsComments|-- [[User:Jean Christophe Trotin|Jean Christophe Trotin]] ([[User talk:Jean Christophe Trotin|talk]]) 11:02, 7 April 2023 (CEST)<br />This version takes into account the "new" [[Contributors:Internal_peripheral_article_model|internal peripheral model]]: | |||

* Take the opportunity of this review by the experts to verify that the content is still pertinent | |||

* Cross-check particularly the assignment tables | |||

The main writer of the article takes the ownership of the review by the experts.<br /> | |||

Remove this comment at the latest before the article is published.}} | |||

==Article purpose== | ==Article purpose== | ||

The purpose of this article is to: | The purpose of this article is to: | ||

* briefly introduce the NVIC and its main features | * briefly introduce the NVIC peripheral and its main features, | ||

* indicate the | * indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts), | ||

* explain how the | * list the software frameworks and drivers managing the peripheral, | ||

* explain how to configure the peripheral. | |||

==Peripheral overview== | ==Peripheral overview== | ||

The '''NVIC''' is the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 interrupt controller. As a result, it cannot be accessed by the Arm Cortex-A7 core. | The '''NVIC''' peripheral is the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 interrupt controller. As a result, it cannot be accessed by the Arm Cortex-A7 core. | ||

Refer to the [[STM32MP15 resources#Reference manuals|STM32MP15 reference manuals]] for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented. | |||

Refer to [[STM32MP15 resources#Reference manuals|STM32MP15 reference manuals]] for the complete list of features, and to the software | |||

== | ==Peripheral usage== | ||

This chapter is applicable in the scope of the '''OpenSTLinux BSP''' running on the Arm<sup>®</sup> Cortex<sup>®</sup>-A processor(s), and the '''STM32CubeMPU Package''' running on the Arm<sup>®</sup> Cortex<sup>®</sup>-M processor. | |||

== | ===Boot time assignment=== | ||

=== | ====On {{MicroprocessorDevice | device=15}}==== | ||

The NVIC can be configured through the [[STM32CubeMP1 architecture|STM32Cube]]. | The NVIC can be configured through the [[STM32CubeMP1 architecture|STM32Cube]]. | ||

{{#lst:STM32MP1_internal_peripherals_assignment_table_template|stm32mp1_boottime}} | |||

<section begin=stm32mp15_boottime /> | |||

| rowspan="1" | Core/Interrupts | |||

| rowspan="1" | [[NVIC internal peripheral|NVIC]] | |||

| NVIC | |||

| | |||

| | |||

| | |||

| | |||

|- | |||

<section end=stm32mp15_boottime /> | |||

|} | |||

===Runtime=== | ===Runtime assignment=== | ||

==== | ====On {{MicroprocessorDevice | device=15}}==== | ||

{{#lst:STM32MP1_internal_peripherals_assignment_table_template|stm32mp15_runtime}} | |||

<section begin=stm32mp15_runtime /> | |||

| rowspan="1" | Core/Interrupts | |||

| rowspan="1" | [[NVIC internal peripheral|NVIC]] | |||

| NVIC | |||

| | |||

| | |||

| <span title="system peripheral" style="font-size:21px">✓</span> | |||

| | |||

|- | |||

<section end=stm32mp15_runtime /> | |||

|} | |||

==Software frameworks and drivers== | |||

Below are listed the software frameworks and drivers managing the NVIC peripheral for the embedded software components listed in the above tables. | |||

* '''STM32Cube''': [[STM32CubeMP1 architecture|NVIC HAL driver]] | |||

* '''TF-A BL2''': {{Highlight|to be completed (or removed) in link with the [[#Boot time assignment|boot time assignment]]}} | |||

* '''U-Boot''': {{Highlight|to be completed (or removed) in link with the [[#Boot time assignment|boot time assignment]]}} | |||

==== | ==How to assign and configure the peripheral== | ||

The peripheral assignment can be done via the [[STM32CubeMX]] graphical tool (and manually completed if needed).<br /> | |||

This tool also helps to configure the peripheral: | |||

* partial device trees (pin control and clock tree) generation for the OpenSTLinux software components, | |||

* HAL initialization code generation for the STM32CubeMPU Package. | |||

The configuration is applied by the firmware running in the context in which the peripheral is assigned. | |||

<noinclude> | <noinclude> | ||

[[Category:Interrupts peripherals]] | [[Category:Interrupts peripherals]] | ||

{{ArticleBasedOnModel| Internal peripheral article model}} | |||

{{PublicationRequestId | 8860 | 2018-09-21 | AnneJ}} | {{PublicationRequestId | 8860 | 2018-09-21 | AnneJ}} | ||

</noinclude> | </noinclude> | ||

Revision as of 11:02, 7 April 2023

1. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the NVIC peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

2. Peripheral overview[edit | edit source]

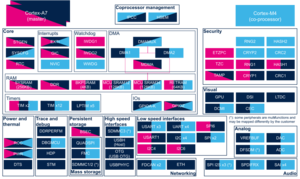

The NVIC peripheral is the Arm® Cortex®-M4 interrupt controller. As a result, it cannot be accessed by the Arm Cortex-A7 core.

Refer to the STM32MP15 reference manuals for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

3. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the STM32CubeMPU Package running on the Arm® Cortex®-M processor.

3.1. Boot time assignment[edit | edit source]

3.1.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

The NVIC can be configured through the STM32Cube.

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 nonsecure (U-Boot) | |||

| Core/Interrupts | NVIC | NVIC | ||||

3.2. Runtime assignment[edit | edit source]

3.2.1. On STM32MP15x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 nonsecure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Core/Interrupts | NVIC | NVIC | ✓ | |||

4. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the NVIC peripheral for the embedded software components listed in the above tables.

- STM32Cube: NVIC HAL driver

- TF-A BL2: to be completed (or removed) in link with the boot time assignment

- U-Boot: to be completed (or removed) in link with the boot time assignment

5. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.