Registered User mNo edit summary |

Registered User No edit summary |

||

| (25 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

This article lists all internal peripherals embedded in | {{ApplicableFor | ||

|MPUs list=STM32MP15x | |||

|MPUs checklist=STM32MP13x, STM32MP15x, STM32MP21x, STM32MP23x, STM32MP25x | |||

}} | |||

<noinclude></noinclude> | |||

This article lists all internal peripherals embedded in {{MicroprocessorDevice | device=15}} and shows the assignment possibilities to the execution contexts for each one of them.<br> | |||

From this article, you can also access to individual peripheral articles in which information related to the overview and configuration can be found. | |||

==Internal peripherals overview== | ==Internal peripherals overview== | ||

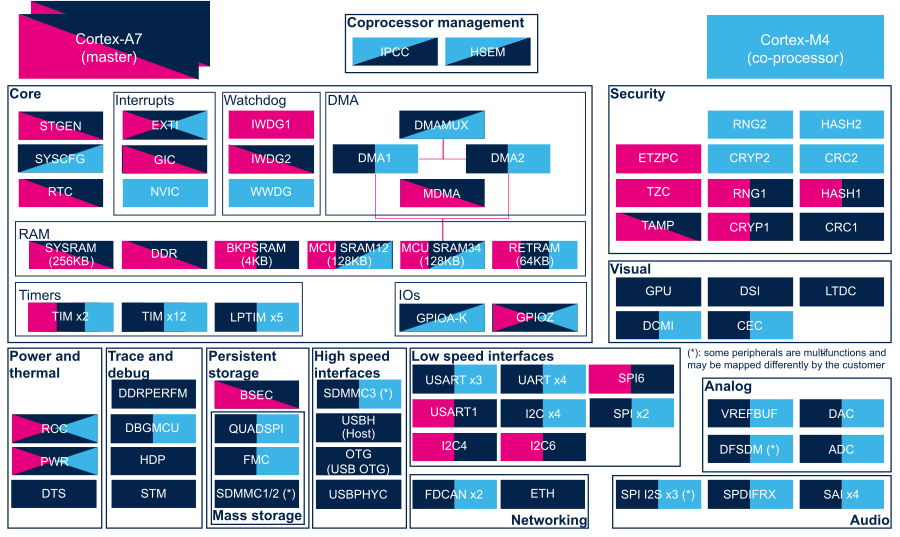

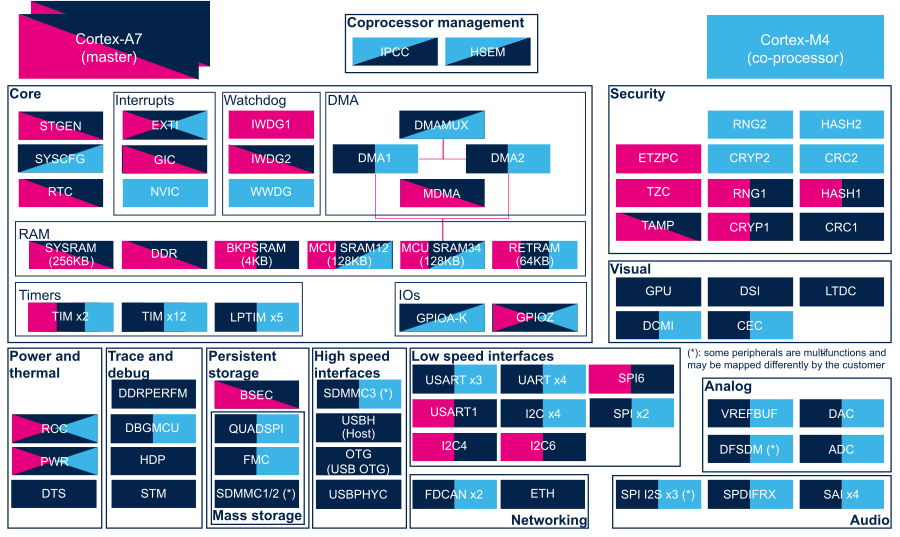

The figure below shows all '''peripherals''' embedded in | The figure below shows all '''peripherals''' embedded in {{MicroprocessorDevice | device=15}}, grouped per '''functional domains''' that are reused in many places of this wiki to structure the articles. | ||

<br /> | <br /> | ||

Several ''' | Several '''execution contexts''' exist on {{MicroprocessorDevice | device=15}}<ref>[[:Category:STM32_MPU_microprocessor_devices#Multiple-core_architecture_concepts|STM32 MPU microprocessor devices: multiple-core architecture concepts]]</ref>, corresponding to the different '''Arm cores and associated security modes''': | ||

* <span style="color:#FFFFFF; background:{{STPink}};"> Arm dual core Cortex-A7 secure </span> (Trustzone), running | * <span style="color:#FFFFFF; background:{{STPink}};"> Arm dual core Cortex-A7 secure </span> (Trustzone), running [[STM32 MPU ROM code overview|ROM code]] and [[TF-A BL2 overview|TF-A BL2]] at boot time, and running [[STM32 MPU OP-TEE overview|OP-TEE]] at runtime | ||

* <span style="color:#FFFFFF; background:{{STDarkBlue}};"> Arm dual core Cortex-A7 non secure </span>, running [[STM32MP15 Linux kernel overview|Linux]] | * <span style="color:#FFFFFF; background:{{STDarkBlue}};"> Arm dual core Cortex-A7 non secure </span>, running [[U-Boot overview|U-Boot]] at boot time, and running [[STM32MP15 Linux kernel overview|Linux]] at runtime | ||

* <span style="color:#FFFFFF; background:{{STLightBlue}};"> Arm Cortex-M4 </span> | * <span style="color:#FFFFFF; background:{{STLightBlue}};"> Arm Cortex-M4 non-secure </span>, running [[STM32CubeMP15 Package architecture|STM32Cube]] | ||

<br /> | <br /> | ||

Some peripherals can be strictly '''assigned''' to one | |||

Other ones can be '''shared''' between several | Some peripherals can be strictly '''assigned''' to one execution context: this is the case for most of the peripherals, like [[USART internal peripheral|USART]] or [[I2C internal peripheral|I2C]].<br /> | ||

Other ones can be '''shared''' between several execution contexts: this is the case for system peripherals, like [[STM32MP15 PWR internal peripheral|PWR]] or [[RCC internal peripheral|RCC]].<br /> | |||

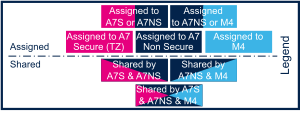

The legend below shows how assigned and shared peripherals are identified in the assignment diagram that follows: | The legend below shows how assigned and shared peripherals are identified in the assignment diagram that follows: | ||

<br /> | |||

[[File: STM32MP1IPsOverview legend.png]] | [[File: STM32MP1IPsOverview legend.png]] | ||

<br /> | |||

Both the diagram below and the following summary table (in [[#Internal peripherals assignment|Internal peripherals assignment]] | Both the diagram below and the following summary table (in [[#Internal peripherals runtime assignment|Internal peripherals runtime assignment]] and [[#Internal peripherals boot time assignment|Internal peripherals boot time assignment]] chapters below) are clickable in order to jump to each peripheral overview articles and get more detailed information (like software frameworks used to control them). | ||

They list STMicroelectronics recommendations. The STM32MP15 reference manual <ref>[[STM32MP15 resources#Reference manuals|STM32MP15 reference manuals]]</ref> may expose more possibilities than what is shown here. | They list STMicroelectronics recommendations. The STM32MP15 reference manual <ref>[[STM32MP15 resources#Reference manuals|STM32MP15 reference manuals]]</ref> may expose more possibilities than what is shown here. | ||

{{ImageMap | Image:STM32MP1IPsOverview.png {{!}} frame {{!}} center{{!}} STM32MP1 internal peripherals overview | |||

{{ | rect 18 14 198 79 [[Arm Cortex-A7 | Cortex-A7]] | ||

ImageMap| | rect 705 12 882 78 [[Arm Cortex-M4 | Cortex-M4]] | ||

Image:STM32MP1IPsOverview.png {{!}} frame {{!}} center{{!}} STM32MP1 internal peripherals overview | |||

rect 18 113 103 141[[STGEN internal peripheral | STGEN]] | rect 18 113 103 141[[STGEN internal peripheral | STGEN]] | ||

rect 18 146 103 175[[ | rect 18 146 103 175[[SYSCFG internal peripheral | SYSCFG]] | ||

rect 18 181 103 208[[ | rect 18 181 103 208[[RTC internal peripheral | RTC]] | ||

rect 123 113 206 141[[EXTI internal peripheral | EXTI]] | rect 123 113 206 141[[EXTI internal peripheral | EXTI]] | ||

rect 123 146 206 175[[GIC internal peripheral | GIC]] | rect 123 146 206 175[[GIC internal peripheral | GIC]] | ||

rect 123 181 206 208[[NVIC internal peripheral | NVIC]] | rect 123 181 206 208[[NVIC internal peripheral | NVIC]] | ||

rect | rect 229 110 314 139[[IWDG internal peripheral | IWDG]] | ||

rect | rect 229 146 314 173[[IWDG internal peripheral | IWDG]] | ||

rect | rect 229 181 314 206[[WWDG internal peripheral | WWDG]] | ||

rect 333 | rect 333 144 417 172[[DMA internal peripheral | DMA]] | ||

rect | rect 466 144 549 172[[DMA internal peripheral | DMA]] | ||

rect 400 | rect 400 111 484 138[[DMAMUX internal peripheral | DMAMUX]] | ||

rect 400 181 484 | rect 400 181 484 206[[MDMA internal peripheral | MDMA]] | ||

rect 29 | rect 29 241 113 268[[SYSRAM internal memory | SYSRAM]] | ||

rect | rect 122 241 206 268[[DDRCTRL and DDRPHYC internal peripherals| DDR via DDR CTRL]] | ||

rect | rect 214 241 298 268[[BKPSRAM internal memory| BKPSRAM]] | ||

rect 307 | rect 307 241 392 268[[STM32MP15 MCU SRAM internal memory | MCU SRAM]] | ||

rect 400 | rect 400 241 484 268[[STM32MP15 MCU SRAM internal memory | MCU SRAM]] | ||

rect | rect 492 241 577 268[[RETRAM internal memory| RETRAM]] | ||

rect 28 | rect 28 304 113 331[[TIM internal peripheral | TIM]] | ||

rect 122 | rect 122 304 207 331[[TIM internal peripheral | TIM]] | ||

rect 214 | rect 214 304 298 331[[LPTIM internal peripheral | LPTIM]] | ||

rect 400 | rect 400 304 484 331[[GPIO internal peripheral | GPIO]] | ||

rect 492 | rect 492 304 577 331[[GPIO internal peripheral | GPIO]] | ||

rect | rect 352 37 438 65 [[IPCC internal peripheral | IPCC]] | ||

rect | rect 445 37 531 65 [[HSEM internal peripheral | HSEM]] | ||

rect 13 | rect 13 415 97 442 [[RCC internal peripheral | RCC]] | ||

rect 13 | rect 13 448 97 474 [[STM32MP15 PWR internal peripheral | PWR]] | ||

rect 13 | rect 13 480 97 508 [[DTS internal peripheral | DTS]] | ||

rect | rect 111 379 195 409 [[DDRPERFM internal peripheral | DDRPERFM]] | ||

rect | rect 111 415 195 442 [[DBGMCU internal peripheral | DBGMCU]] | ||

rect | rect 111 448 195 474 [[HDP internal peripheral | HDP]] | ||

rect 215 | rect 215 381 298 408 [[BSEC internal peripheral | BSEC]] | ||

rect 215 | rect 215 415 298 442 [[QUADSPI internal peripheral | QUADSPI]] | ||

rect 215 | rect 215 448 298 474 [[FMC internal peripheral | FMC]] | ||

rect | rect 215 480 298 508 [[SDMMC internal peripheral | SDMMC]] | ||

rect | rect 413 480 496 508 [[FDCAN internal peripheral | FDCAN]] | ||

rect 501 | rect 501 480 584 508 [[ETH internal peripheral | ETH]] | ||

rect 316 | rect 316 381 401 408 [[SDMMC internal peripheral | SDMMC]] | ||

rect 316 | rect 316 415 401 442 [[USBH internal peripheral | USBH]] | ||

rect 316 | rect 316 448 401 474 [[OTG internal peripheral | OTG]] | ||

rect 316 | rect 316 480 401 508 [[USBPHYC internal peripheral | USBPHYC]] | ||

rect 413 | rect 413 365 496 393 [[USART internal peripheral | USART]] | ||

rect 413 | rect 413 400 496 426[[USART internal peripheral | USART]] | ||

rect | rect 501 365 585 393 [[USART internal peripheral | USART]] | ||

rect 413 | rect 413 434 496 460 [[I2C internal peripheral | I2C]] | ||

rect | rect 501 400 585 426 [[I2C internal peripheral | I2C]] | ||

rect | rect 501 434 585 460 [[I2C internal peripheral | I2C]] | ||

rect 591 | rect 591 365 674 393 [[SPI internal peripheral | SPI]] | ||

rect 591 | rect 591 400 674 426 [[SPI internal peripheral | SPI]] | ||

rect | rect 708 111 792 138 [[RNG internal peripheral | RNG]] | ||

rect 800 | rect 800 111 883 138 [[HASH internal peripheral | HASH]] | ||

rect | rect 616 144 700 172 [[ETZPC internal peripheral | ETZPC]] | ||

rect | rect 708 144 792 172 [[CRYP internal peripheral | CRYP]] | ||

rect 800 | rect 800 144 883 172 [[CRC internal peripheral | CRC]] | ||

rect 617 | rect 617 179 701 206 [[TZC internal peripheral | TZC]] | ||

rect | rect 708 179 792 206 [[RNG internal peripheral | RNG]] | ||

rect 800 | rect 800 179 883 206 [[HASH internal peripheral | HASH]] | ||

rect 617 | rect 617 213 701 240 [[TAMP internal peripheral | TAMP]] | ||

rect 709 | rect 709 213 792 240 [[CRYP internal peripheral | CRYP]] | ||

rect 800 | rect 800 213 883 240 [[CRC internal peripheral | CRC]] | ||

rect 617 | rect 617 278 700 306 [[GPU internal peripheral | GPU]] | ||

rect 709 | rect 709 278 792 306 [[DSI internal peripheral | DSI]] | ||

rect 800 | rect 800 278 883 306 [[LTDC internal peripheral | LTDC]] | ||

rect 617 | rect 617 312 700 338 [[DCMI internal peripheral | DCMI]] | ||

rect 709 | rect 709 312 792 338 [[CEC internal peripheral | CEC]] | ||

rect 709 | rect 709 400 792 426 [[STM32MP15 VREFBUF internal peripheral | VREFBUF]] | ||

rect 800 | rect 800 400 883 426 [[DAC internal peripheral | DAC]] | ||

rect 709 | rect 709 436 792 462 [[DFSDM internal peripheral | DFSDM]] | ||

rect 800 | rect 800 436 883 462 [[STM32MP15 ADC internal peripheral | ADC]] | ||

rect | rect 617 481 700 508 [[SPI internal peripheral | SPI I2S]] | ||

rect 709 | rect 709 481 792 508 [[SPDIFRX internal peripheral | SPDIFRX]] | ||

rect 800 | rect 800 481 883 508 [[SAI internal peripheral | SAI]] | ||

}} | }} | ||

==Internal peripherals assignment== | ==Internal peripherals runtime assignment== | ||

{{: | {{#lst:STM32MP1_internal_peripherals_assignment_table_template|stm32mp15_runtime}} | ||

{{:STM32MP15_ADC_internal_peripheral}} | {{#lst:STM32MP15_ADC_internal_peripheral|stm32mp15_runtime}} | ||

{{:DAC_internal_peripheral}} | {{#lst:DAC_internal_peripheral|stm32mp15_runtime}} | ||

{{: | {{#lst:DFSDM_internal_peripheral|stm32mp15_runtime}} | ||

{{:STM32MP15_VREFBUF_internal_peripheral}} | {{#lst:STM32MP15_VREFBUF_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:SAI internal peripheral| | {{#lst:SAI internal peripheral|stm32mp15_runtime}} | ||

{{#lst:SPDIFRX internal peripheral| | {{#lst:SPDIFRX internal peripheral|stm32mp15_runtime}} | ||

{{:IPCC_internal_peripheral}} | {{#lst:IPCC_internal_peripheral|stm32mp15_runtime}} | ||

{{:HSEM_internal_peripheral}} | {{#lst:HSEM_internal_peripheral|stm32mp15_runtime}} | ||

{{: | {{#lst:RTC_internal_peripheral|stm32mp15_runtime}} | ||

{{:STGEN_internal_peripheral}} | {{#lst:STGEN_internal_peripheral|stm32mp15_runtime}} | ||

{{: | {{#lst:SYSCFG_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:DMA_internal_peripheral| | {{#lst:DMA_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:DMAMUX_internal_peripheral| | {{#lst:DMAMUX_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:MDMA_internal_peripheral| | {{#lst:MDMA_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:EXTI_internal_peripheral| | {{#lst:EXTI_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:GIC_internal_peripheral| | {{#lst:GIC_internal_peripheral|stm32mp15_runtime}} | ||

{{:NVIC_internal_peripheral}} | {{#lst:NVIC_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:GPIO internal peripheral| | {{#lst:GPIO internal peripheral|stm32mp15_runtime}} | ||

{{#lst:BKPSRAM internal memory| | {{#lst:BKPSRAM internal memory|stm32mp15_runtime}} | ||

{{#lst:DDRCTRL and DDRPHYC internal peripherals| | {{#lst:DDRCTRL and DDRPHYC internal peripherals|stm32mp15_runtime}} | ||

{{: | {{#lst:STM32MP15_MCU_SRAM_internal_memory|stm32mp15_runtime}} | ||

{{:RETRAM internal memory}} | {{#lst:RETRAM internal memory|stm32mp15_runtime}} | ||

{{#lst:SYSRAM_internal_memory| | {{#lst:SYSRAM_internal_memory|stm32mp15_runtime}} | ||

{{#lst:LPTIM_internal_peripheral| | {{#lst:LPTIM_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:TIM_internal_peripheral| | {{#lst:TIM_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:IWDG_internal_peripheral| | {{#lst:IWDG_internal_peripheral|stm32mp15_runtime}} | ||

{{:WWDG_internal_peripheral}} | {{#lst:WWDG_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:OTG_internal_peripheral| | {{#lst:OTG_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:USBH_internal_peripheral| | {{#lst:USBH_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:USBPHYC internal peripheral| | {{#lst:USBPHYC internal peripheral|stm32mp15_runtime}} | ||

{{#lst:I2C_internal_peripheral| | {{#lst:I2C_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:SPI_internal_peripheral| | {{#lst:SPI_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:USART_internal_peripheral| | {{#lst:USART_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:FMC internal peripheral| | {{#lst:FMC internal peripheral|stm32mp15_runtime}} | ||

{{#lst:QUADSPI internal peripheral| | {{#lst:QUADSPI internal peripheral|stm32mp15_runtime}} | ||

{{#lst:SDMMC internal peripheral| | {{#lst:SDMMC internal peripheral|stm32mp15_runtime}} | ||

{{#lst:ETH internal peripheral| | {{#lst:ETH internal peripheral|stm32mp15_runtime}} | ||

{{#lst:FDCAN internal peripheral| | {{#lst:FDCAN internal peripheral|stm32mp15_runtime}} | ||

{{#lst:DTS_internal_peripheral| | {{#lst:DTS_internal_peripheral|stm32mp15_runtime}} | ||

{{:STM32MP15_PWR_internal_peripheral}} | {{#lst:STM32MP15_PWR_internal_peripheral|stm32mp15_runtime}} | ||

{{: | {{#lst:RCC_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:BSEC_internal_peripheral| | {{#lst:BSEC_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:CRC_internal_peripheral| | {{#lst:CRC_internal_peripheral|stm32mp15_runtime}} | ||

{{: | {{#lst:CRYP_internal_peripheral|stm32mp15_runtime}} | ||

{{: | {{#lst:ETZPC_internal_peripheral|stm32mp15_runtime}} | ||

{{: | {{#lst:HASH_internal_peripheral|stm32mp15_runtime}} | ||

{{: | {{#lst:RNG_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:TZC_internal_peripheral| | {{#lst:TZC_internal_peripheral|stm32mp15_runtime}} | ||

{{: | {{#lst:TAMP_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:DBGMCU_internal_peripheral| | {{#lst:DBGMCU_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:HDP_internal_peripheral| | {{#lst:DDRPERFM_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst: | {{#lst:HDP_internal_peripheral|stm32mp15_runtime}} | ||

{{: | {{#lst:CEC_internal_peripheral|stm32mp15_runtime}} | ||

{{:CEC_internal_peripheral}} | {{#lst:DCMI_internal_peripheral|stm32mp15_runtime}} | ||

{{:DCMI_internal_peripheral}} | {{#lst:DSI_internal_peripheral|stm32mp15_runtime}} | ||

{{:DSI_internal_peripheral}} | {{#lst:GPU_internal_peripheral|stm32mp15_runtime}} | ||

{{:GPU_internal_peripheral}} | {{#lst:LTDC_internal_peripheral|stm32mp15_runtime}} | ||

{{#lst:LTDC_internal_peripheral| | |} | ||

==Internal peripherals boot time assignment== | |||

{{#lst:STM32MP1_internal_peripherals_assignment_table_template|stm32mp1_boottime}} | |||

{{#lst:STM32MP15_ADC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:DAC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:DFSDM_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:STM32MP15_VREFBUF_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:SAI internal peripheral|stm32mp15_boottime}} | |||

{{#lst:SPDIFRX internal peripheral|stm32mp15_boottime}} | |||

{{#lst:IPCC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:HSEM_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:RTC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:STGEN_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:SYSCFG_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:DMA_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:DMAMUX_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:MDMA_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:EXTI_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:GIC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:NVIC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:GPIO internal peripheral|stm32mp15_boottime}} | |||

{{#lst:BKPSRAM internal memory|stm32mp15_boottime}} | |||

{{#lst:DDRCTRL and DDRPHYC internal peripherals|stm32mp15_boottime}} | |||

{{#lst:STM32MP15_MCU_SRAM_internal_memory|stm32mp15_boottime}} | |||

{{#lst:RETRAM internal memory|stm32mp15_boottime}} | |||

{{#lst:SYSRAM_internal_memory|stm32mp15_boottime}} | |||

{{#lst:LPTIM_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:TIM_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:IWDG_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:WWDG_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:OTG_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:USBH_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:USBPHYC internal peripheral|stm32mp15_boottime}} | |||

{{#lst:I2C_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:SPI_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:USART_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:FMC internal peripheral|stm32mp15_boottime}} | |||

{{#lst:QUADSPI internal peripheral|stm32mp15_boottime}} | |||

{{#lst:SDMMC internal peripheral|stm32mp15_boottime}} | |||

{{#lst:ETH internal peripheral|stm32mp15_boottime}} | |||

{{#lst:FDCAN internal peripheral|stm32mp15_boottime}} | |||

{{#lst:DTS_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:STM32MP15_PWR_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:RCC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:BSEC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:CRC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:CRYP_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:ETZPC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:HASH_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:RNG_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:TZC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:TAMP_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:DBGMCU_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:DDRPERFM_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:HDP_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:CEC_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:DCMI_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:DSI_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:GPU_internal_peripheral|stm32mp15_boottime}} | |||

{{#lst:LTDC_internal_peripheral|stm32mp15_boottime}} | |||

|} | |} | ||

| Line 168: | Line 235: | ||

{{PublicationRequestId | 9171 | 2018-10-17 | AlainF}} | {{PublicationRequestId | 9171 | 2018-10-17 | AlainF}} | ||

[[Category:Peripherals overview]] | [[Category:Peripherals overview]] | ||

</noinclude> | </noinclude> | ||

Latest revision as of 15:58, 8 October 2024

This article lists all internal peripherals embedded in STM32MP15x lines ![]() and shows the assignment possibilities to the execution contexts for each one of them.

and shows the assignment possibilities to the execution contexts for each one of them.

From this article, you can also access to individual peripheral articles in which information related to the overview and configuration can be found.

1. Internal peripherals overview

The figure below shows all peripherals embedded in STM32MP15x lines ![]() , grouped per functional domains that are reused in many places of this wiki to structure the articles.

, grouped per functional domains that are reused in many places of this wiki to structure the articles.

Several execution contexts exist on STM32MP15x lines ![]() [1], corresponding to the different Arm cores and associated security modes:

[1], corresponding to the different Arm cores and associated security modes:

- Arm dual core Cortex-A7 secure (Trustzone), running ROM code and TF-A BL2 at boot time, and running OP-TEE at runtime

- Arm dual core Cortex-A7 non secure , running U-Boot at boot time, and running Linux at runtime

- Arm Cortex-M4 non-secure , running STM32Cube

Some peripherals can be strictly assigned to one execution context: this is the case for most of the peripherals, like USART or I2C.

Other ones can be shared between several execution contexts: this is the case for system peripherals, like PWR or RCC.

The legend below shows how assigned and shared peripherals are identified in the assignment diagram that follows:

Both the diagram below and the following summary table (in Internal peripherals runtime assignment and Internal peripherals boot time assignment chapters below) are clickable in order to jump to each peripheral overview articles and get more detailed information (like software frameworks used to control them). They list STMicroelectronics recommendations. The STM32MP15 reference manual [2] may expose more possibilities than what is shown here.

- Cortex-A7

- Cortex-M4

- STGEN

- SYSCFG

- RTC

- EXTI

- GIC

- NVIC

- IWDG

- WWDG

- DMA

- DMAMUX

- MDMA

- SYSRAM

- DDR via DDR CTRL

- BKPSRAM

- MCU SRAM

- RETRAM

- TIM

- LPTIM

- GPIO

- IPCC

- HSEM

- RCC

- PWR

- DTS

- DDRPERFM

- DBGMCU

- HDP

- BSEC

- QUADSPI

- FMC

- SDMMC

- FDCAN

- ETH

- USBH

- OTG

- USBPHYC

- USART

- I2C

- SPI

- RNG

- HASH

- ETZPC

- CRYP

- CRC

- TZC

- TAMP

- GPU

- DSI

- LTDC

- DCMI

- CEC

- VREFBUF

- DAC

- DFSDM

- ADC

- SPI I2S

- SPDIFRX

- SAI

2. Internal peripherals runtime assignment

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Analog | DFSDM | DFSDM | ☐ | ☐ | Assignment (single choice) | |

| Core | RTC | RTC | ☑ | ☐ | ☐ | RTC is mandatory to resynchronize STGEN after exiting low-power modes. |

| Core | SYSCFG | SYSCFG | ☑ | ☑ | ☑ | |

| Core/RAM | MCU SRAM | SRAM1 | ☐ | ☐ | ☐ | Assignment (between A7 S and A7 NS / M4) Shareable (between A7 NS and M4) |

| SRAM2 | ☐ | ☐ | ☐ | Assignment (between A7 S and A7 NS / M4) Shareable (between A7 NS and M4) | ||

| SRAM3 | ☐ | ☐ | ☐ | Assignment (between A7 S and A7 NS / M4) Shareable (between A7 NS and M4) | ||

| SRAM4 | ☐ | ☐ | ☐ | Assignment (between A7 S and A7 NS / M4) Shareable (between A7 NS and M4) | ||

| Power & Thermal | RCC | RCC | ✓ | ✓ | ✓ | |

| Security | CRYP | CRYP1 | ☐ | ☐ | Assignment (single choice) | |

| CRYP2 | ☐ | |||||

| Security | ETZPC | ETZPC | ✓ | ✓ | ⬚ | |

| Security | HASH | HASH1 | ☐ | ☐ | Assignment (single choice) | |

| HASH2 | ☐ | |||||

| Security | RNG | RNG1 | ☐ | ☐ | Assignment (single choice) | |

| RNG2 | ☐ | |||||

| Security | TAMP | TAMP | ☑ | ☑ | ☐ | |

| Trace & Debug | DDRPERFM | DDRPERFM | ☐ | |||

3. Internal peripherals boot time assignment

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (ROM code) |

Cortex-A7 secure (TF-A BL2) |

Cortex-A7 non-secure (U-Boot) | |||

| Core | RTC | RTC | ☐ | |||

| Core | SYSCFG | SYSCFG | ✓ | ☑ | ☑ | |

| Core/RAM | MCU SRAM | Any instance | ✓ | ☑ | ☐ | |

| Power & Thermal | RCC | RCC | ✓ | ✓ | ✓ | |

| Security | ETZPC | Any instance | ✓ | ✓ | ✓ | ETZPC configuration is set by OP-TEE |

| Security | HASH | HASH1 | ✓ | ☑ | ||

| HASH2 | not used at boot time. | |||||

| Security | RNG | RNG1 | ☑ | ☐ | ||

| Security | TAMP | TAMP | ✓ | ☑ | ☑ | |

4. References