The purpose of this article is to:

- Give an overview of the external memory

- Briefly introduce the QuadSPI, OctoSPI, HSPI and XSPI controllers integrated within the STM32 microcontrollers (MCUs).

- Explain how to configure the peripheral

- List all the available resources to help users get started

1. Acronyms and definitions

| Term | Definition |

|---|---|

| DTR | Double data rate |

| HSPI | Hexadeca Serial Peripheral Interface |

| OCTOSPI | Octal Serial Peripheral Interface |

| OCTOSPIM | OCTOSPI IO manager |

| QUADSPI | Quad Serial Peripheral Interface |

| SDR | Single data rate |

| XSPI | Extended Serial Peripheral Interface |

| XSPIM | XSPI IO manager |

2. What is external Memory?

As application complexity increases, driven by the demand for richer, more intuitive graphical user interfaces (GUIs) and human-machine interfaces (HMIs), as well as advanced processing capabilities such as big data and artificial intelligence (AI), and especially the need for additional space to perform future firmware upgrades, these requirements impose additional demands on the often-limited on-chip memory of microcontroller units (MCUs). To overcome the constraints of on-chip memory, the implementation of external memory is a viable solution for expanding storage capacity and enhancing overall system performance.

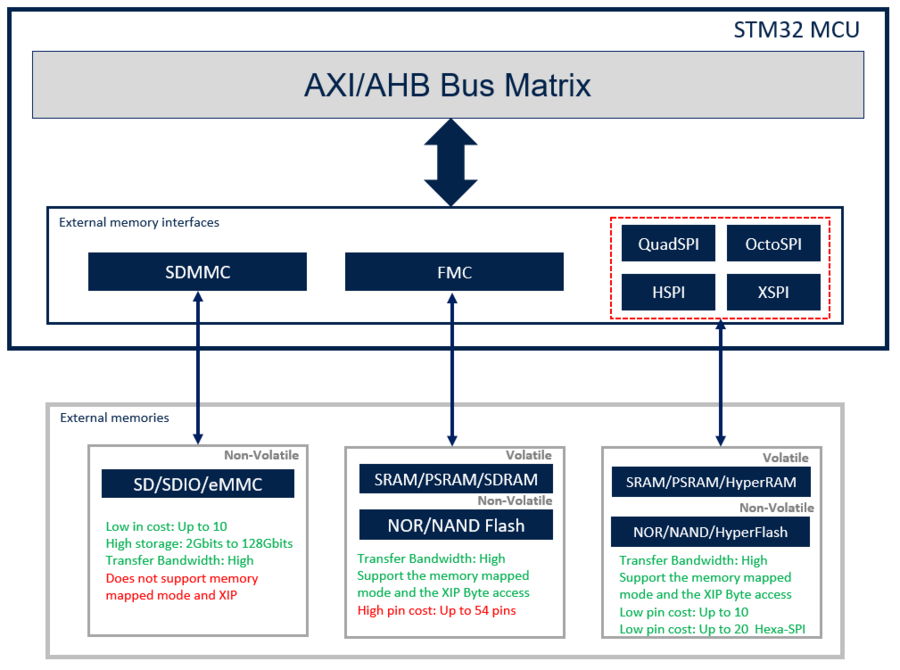

To meet these demands, STMicroelectronics offers a range of MCUs that integrate advanced external serial memory controllers. These controllers enable seamless interfacing and communication with external memories. The controllers, including SDMMC, FMC, QUADSPI, OCTOSPI, HSPI, and XSPI, are designed to support various types of external memories, thereby addressing the limitations of on-chip memory, ensuring high data throughputs, and providing greater flexibility for designers, particularly for new Flash-less MCUs.

The diagram below provides a brief overview of the external memories.

Non-Volatile vs. Volatile External Memory

- Non-Volatile memory is mainly used for storing some or all graphical data assets, such as bitmaps, fonts, translations, and TouchGFx application code.

- External volatile memory, on the other hand, is used to for storing the framebuffer(s) and code content.

The primary aim of this article is not to delve into every interface in detail, but to provide the essential documentation related to these interfaces. This ensures that users can find all the necessary information to start their application with these interfaces without having to search extensively. This article focuses on the QuadSPI, OctoSPI, HSPI, and XSPI interfaces by giving a brief overview of these interfaces and listing all helpful and related links.

3. QuadSPI, OctoSPI, HSPI and XSPI overview

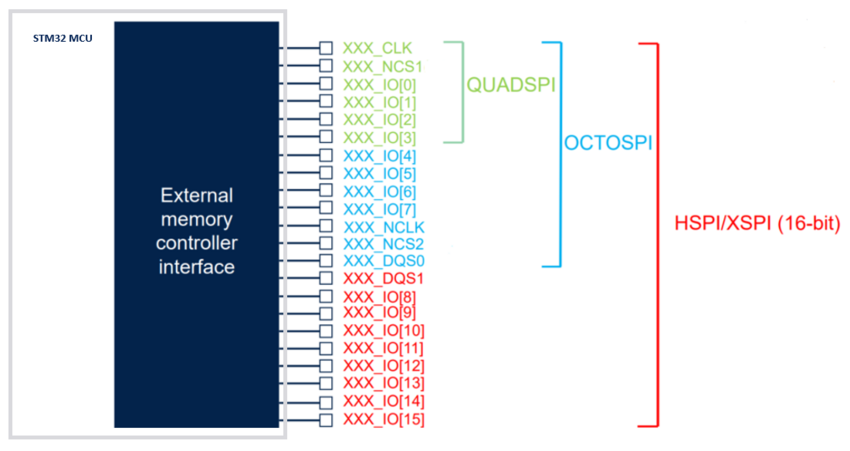

The Quad Serial Peripheral Interface (QUADSPI) is the first interface introduced by STMicroelectronics in the STM32F4 series that allows communication on up to four data lines between the STM32 and an external serial memory. This interface supports single, dual, and quad-SPI memories.

The Octal Serial Peripheral Interface (OCTOSPI) was first introduced in the STM32L4 series to further enhance the QSPI interface by using eight data lines between the STM32 and an external serial memory allowing to interface with octo-SPI memories. This interface supports single, dual, quad-SPI, and octo-SPI memories.

The Hexadeca Serial Peripheral Interface (HSPI), introduced in the STM32U5 series for STM32U59x/5Ax and STM32U5Fx/5Gx devices, extends to 16 I/O data lines the memory interface and can operate up to 160 MHz. In this mode, only the data phase uses a 16-bit line width, while the command and address phases use an 8-bit line width.

The Extended Serial Peripheral Interface (XSPI), introduced in the STM32H7RS series, also employs 16 I/O data lines and can operate up to 200 MHz. This interface is designed to support a wide range of external memory types, ensuring optimal performances and scalability for complex applications. It supports single, dual, quad-SPI, octo-SPI, and 16-bit memories.

Where XXX can be QUADSPI, OCTOSPI, HSPI, XSPI, OCTOSPIM_Px or XSPIM_Px. Refer to the product datasheet and reference manual to see which interface is implemented and the available pins.

Supported Features

These interfaces integrated into STM32 MCUs offer several key features. Below are the main features:

- OCTOSPI, HSPI, and XSPI are designed to support JESD251C, HyperBus™ and Xccela™ protocols

- Functional modes: indirect, automatic status-polling, and memory-mapped

- Indirect mode: In this mode all the operation are performed using the controller registers to preset commands, addresses, data, and transfer parameters

- Automatic status-polling mode: In this mode the external memory status is periodically read, and an interrupt on a matching flag can be generated in case of flag setting. This mode is used only in regular-command protocol, and it depends on whether the external memory supports it (useful for checking the end of the erase or the end of programming)

- Memory mapped-mode: In this mode the external memory device is seen by the system as it was an internal memory, only 256Mbytes can be addressed

- Support eXecute In Place (XIP)

- SDR (Single Data Rate) and DTR (Double Transfer Rate) support

- Data strobe support

- Integrated FIFO for reception and transmission

- 8-, 16-, and 32-bit data accesses allowed

- DMA protocol support

- Interrupt generation on FIFO threshold, timeout, operation complete, and access error

- Supports the following protocols with associated frame formats, allowing compatibility with almost all memory available on the market

- The regular-command frame is the classical frame format where the peripheral communicates with the external memory device by using commands; each command can include the following phases and, at least, one of the five phases must be present.

- Instruction phase

- Address phase

- Alternate-byte phase

- Dummy-cycle phase

- Data Phase

- The HyperBus™ frame format to support HyperRAM™ and HyperFlash™ memories. The HyperBus frame composed of two phases:

- Command/adddess phase (CA)

- Data phase

On the command/address phase, the HyperRam/HyperFlash memory will use the read-recovery time (RWDS) to check if an additional initial access latency has to be inserted. Two modes are available on HyperBus protocol:

- HyperBus memory mode: This mode allows the read/write access from/to HyperBus memory

- HyperBus register mode: This mode allows to access the memory device register space

For a complete list of features refer to the STM32 products reference manuals.

Supported memories

| STM32 Product | Vendor | Memory reference | Voltage (V) | Standard |

|---|---|---|---|---|

| STM32 with QSPI interface | Quad-SPI | |||

| Micron | MT25QL128A | 3 | - | |

| NUMONIX | N25Q256A | 2.7-3.6 | - | |

| Macronix | MX25L5124G | 2.7-3.6 | - | |

| Infineon | S25FS128SIFI000 | 1.8 | - | |

| STM32L4

STM32L5 STM32U5 STM32H5 STM32H7 |

Octo-SPI | |||

| Flash | ||||

| Macronix | MX25UM51245G | 1.8 | OCTABUS | |

| Macronix | MX25LMS51245G | 3-3.3 | OCTABUS | |

| Infineon | S71KL512SC0BHI00 | 3 | Hyper COMBO FLASH/RAM (HyperBus) | |

| RAM | ||||

| APmemory | APS6408L-3OBM-BA | 2.7-3.6 | Xcella | |

| ISSI | IS66WVH8M8BLL-100B1LI | 3 | HyperRAM(HyperBus) | |

| Winbond | W955D8MBYA | 1.7-1.95 | HyperRAM(HyperBus) | |

| STM32U59x/5Ax

STM32U5Fx/5Gx |

HSPI | |||

| APmemory | APS256XXN-OBR-BG | 1.62-1.98 | Xcella | |

| Winbond | W958D6NBMA | 1.7-2.0 | HyperRAM(HyperBus) | |

| STM32H7R/S | XSPI | |||

| Macronix | MX66UW1G45GXDI00 | 1.8 | OCTABUS(NorFlash:Support read while write feature) | |

| APmemory | APS256XXN-OBR-BG | 1.62-1.98 | Xcella | |

4. Configuring peripherals

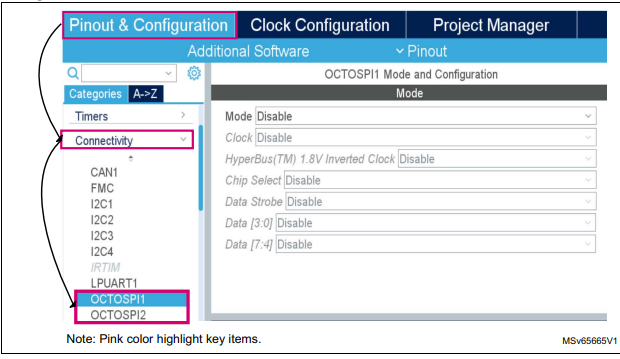

Before any data can be transferred to or from the external memory, the peripheral needs to be configured. This configuration can be accomplished using the STM32CubeMX graphical tool, with additional manual adjustment if needed.

The configuration steps are generally similar for all peripherals, but there is specific difference for the OCTOSPI, HSPI, and XSPI peripherals compared to the QSPI.

Configuration steps

Once The STM32CubeMX is created, the user must follow the steps below:

1. Select Pinout and Configuration tab, under connectivity, select the available peripheral on your desired product 2. Select the memory mode you wish to use, the mode depends on the memory and its communication protocol

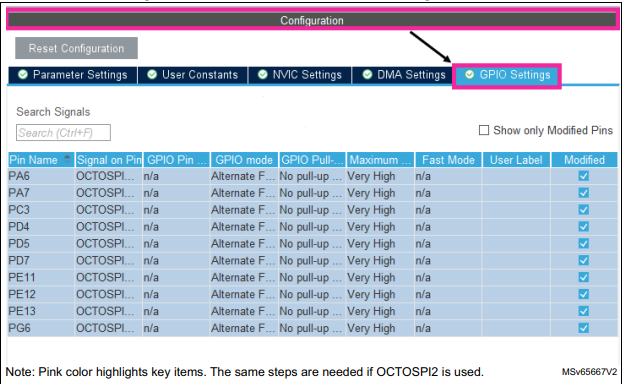

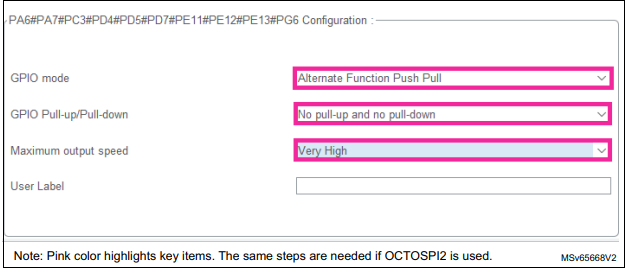

3. Depending on the selected instance select and configure the pins as shown in the figure below. Ensure that the pins used are dedicated for the serial external serial memory controller. Refer to the product datasheet for more details

Make sure that the output speed is set to "Very high" for all the GPIOs.

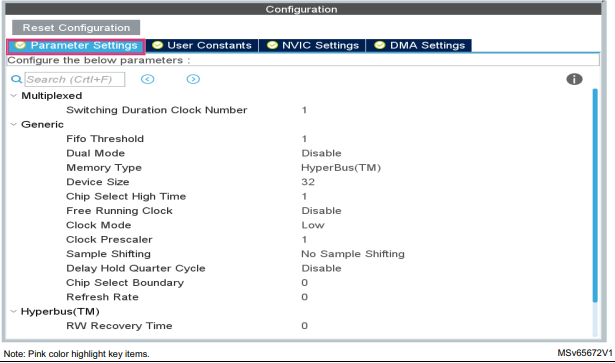

4. Configure the system and the external serial memory controller clock 5. Once all the GPIOs and the clock configuration have been done, the user must configure the controller parameter, these parameters depend on the used memory and its communication protocol

For more details about this step, users can refer to section 7.2.4 'OCTOSPI Configuration and Parameter Settings' of AN5050 or to the following FAQ

5. Security

With the ability to store code/data and perform Over-The-Air (OTA) updates comes the need to protect code and firmware with robust security measures. Ideally, data should be secured where it resides, not just within the processor. Storing code in external memory introduces the necessity to secure the memory interface as well.

To address this, STMicroelectronics is proactively tackling this security challenge by integrating advanced security peripherals when interfacing with external serial memories, such as the OTFDEC and MCE engines.

- The OTFDEC (On-The-Fly Decryption): designed to decrypt encrypted of the Arm® AXI or AHB traffic based on the read request address information.

- The Memory Cipher Engine (MCE): designed to provide encryption and decryption services for data stored in internal or external memory.

For more details about these two features and how they can be used by these interfaces, refer to the following application notes:

How to use OTFDEC for encryption/decryption in trusted environment on STM32H7Bxxx and STM32H73xx microcontrollers OTFDEC

How to use MCE for encryption/decryption on STM32 MCUs MCE

Check the STM32 product datasheets to find out the availably of these peripherals.

6. Recommended PCB Routing Guidelines for External Memory

The speed at which these interfaces operate depends on several factors, including the board layout and pad speeds. With a good layout, it is possible to achieve maximum speeds. Therefore, the layout should be optimized to ensure the best performance. For detailed guidance, refer to the application note "Getting started with STM32H7Rx/7Sx MCUs hardware development" AN5935 available on the STMicroelectronics website, specifically section "10.4.3 Extended-SPI interface (XSPI)".

Please note that each product from STMicroelectronics comes with its specific "Getting Started" guide to help you with the hardware development process.

7. STMicroelectronics resources

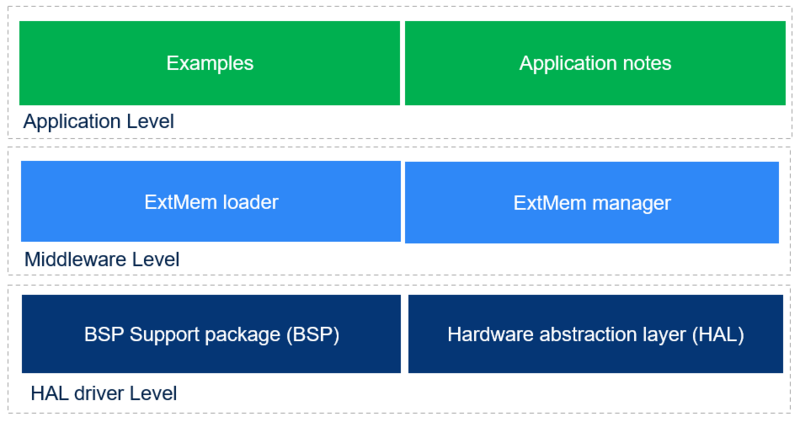

ST provides drivers and middleware, along with extensive examples, to help users understand these controllers and quickly start their applications.

Below is a list of the available resources and their links:

- Applications note:

AN4760 Quad-SPI interface on STM32 microcontrollers and microprocessors

AN5050 Getting started with Octo-SPI, Hexadeca-SPI, and XSPI Interface on STM32 MCU

- Examples

Preconfigured examples for supported MCUs are available to help users get started quickly. These examples can be found under:

STM32Cube_FW_xx\Projects\STM32xxx\Examples\

These examples describe how to use:

- Write and read data in memory-mapped mode in the OCTOSPI HyperRAM memory

- Execute code from NOR/PSRAM memory after code loading

- NOR/PSRAM memory in memory-mapped mode

- NOR/PSRAM memory in DMA mode

- Middleware

Middleware components are provided to streamline the integration and usage of these peripherals in various application. One such component is the External Loader. This middleware facilitates the programming, erasing, and reading of external memory devices without changing the internal flash memory.

ST provides examples loaders for:

- Macronix QuadSPI/OctoSPI NOR Flash

- Micron NOR Flash

External loader examples can be found following this link: Github

For more detailed about the External loader users can refer to the following application note and wiki pages introducing new middleware appearing on the STM32H7RS series to ease the use of external serial NOR memories: Introduction to external memory manager and external memory loader middleware for boot flash MCU AN6101

https://wiki.st.com/stm32mcu/wiki/Introduction_to_External_memory_Manager

https://wiki.st.com/stm32mcu/wiki/Introduction_to_External_memory_Loader

Getting started with External memory Manager and External memory loader

- Drivers

Based on the selected MCU, users can refer to available resources provided in the STM32Cube Firmware package. Drivers and BSP component drivers can be found under:

STM32Cube_FW_xx\Drivers\STM32xxxx_HAL_Driver STM32Cube_FW_xx\Drivers\BSP\Components

ST provides drivers examples for:

- MT25QL128A: https://github.com/STMicroelectronics/stm32-mt25ql512abb

- N25Q256A: https://github.com/STMicroelectronics/stm32-n25q256a

- S25FS128S:https://github.com/STMicroelectronics/stm32-s25fl128s

- MX25UM51245G: https://github.com/search?q=org%3ASTMicroelectronics+MX25UM512&type=repositories

- MX25LM51245G: https://github.com/STMicroelectronics/stm32-mx25lm51245g

- APS6408L: https://github.com/STMicroelectronics/stm32-aps6408

- ISS66WVH8M8: https://github.com/STMicroelectronics/stm32-iss66wvh8m8

- APS256: https://github.com/STMicroelectronics/stm32-aps256

- APS512: https://github.com/STMicroelectronics/stm32-aps512

- MX66UW1G45G: https://github.com/STMicroelectronics/stm32-mx66uw1g45g/blob/main/mx66uw1g45g.c

- Documents related to external serial memory interfaces

- STM32F7 performance software: https://www.st.com/en/embedded-software/x-cube-32f7perf.html

- STM32H7 performance software: https://www.st.com/en/embedded-software/x-cube-perf-h7.html t.com/en/embedded-software/x-cube-perf-h7.html

- STM32H7Rx/7Sx performance software: https://www.st.com/en/embedded-software/x-cube-perf-h7rs.html