1. Article purpose[edit | edit source]

The purpose of this article is to:

- briefly introduce the ADC peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

2. Peripheral overview[edit | edit source]

The ADC peripheral is a successive approximation analog-to-digital converter.

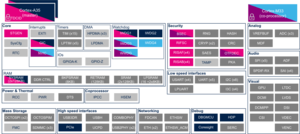

On STM32MP25x lines ![]() , there are three physical ADCs distributed between two ADC blocks:

, there are three physical ADCs distributed between two ADC blocks:

- Each ADC has up to 20 multiplexed channels.

- ADC1 and ADC2 are tightly coupled.

- ADC1 is connected to 18 external channels + 2 internal channels.

- ADC2 is connected to 14 external channels + 6 internal channels.

- ADC3 is controlled independently.

- ADC3 is connected to 14 external channels + 6 internal channels.

- ADC1 and ADC2 are tightly coupled.

- Configurable resolution: 12, 10, 8, 6 bits.

- The conversions can be performed in single, continuous, scan, or discontinuous mode.

- The result can be read in a left-aligned or right-aligned 32-bit data register by using CPU or DMA[1].

- The analog watchdog feature allows the application to detect if the input voltage goes beyond the user-defined high or low thresholds.

- The ADC clock source used for conversions is selected by the RCC[2] independently from the AHB bus clock that is used to access the ADC registers.

- The common reference voltage can be provided by either VREFBUF[3] or any other external regulator[4] wired to VREF+ pin.

Each ADC supports two contexts to manage conversions:

- Regular conversions can be done in sequence, running in the background.

- Injected conversions have a higher priority, and so can interrupt the regular sequence (either triggered in software or hardware). The regular sequence is resumed in case it has been interrupted.

- Each context has its own configurable sequence and trigger: software, TIM[5], LPTIM[6], and EXTI[7].

Refer to the STM32 MPU reference manuals for the complete list of features and to the software frameworks and drivers introduced below to see which features are implemented.

3. Peripheral usage[edit | edit source]

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the STM32CubeMPU Package running on the Arm® Cortex®-M processor.

3.1. Boot time assignment[edit | edit source]

3.1.1. On STM32MP2 series[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

- ⬚ means that the peripheral can be assigned to the given boot time context, but this configuration is not supported in STM32 MPU Embedded Software distribution.

- ☐ means that the peripheral can be assigned to the given boot time context.

- ☑ means that the peripheral is assigned by default to the given boot time context and that the peripheral is mandatory for the STM32 MPU Embedded Software distribution.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP25 reference manuals.

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 non-secure (U-Boot) | |||

| Analog | ADC | ADC12 | ⬚ | ☐ | ||

| ADC3 | ⬚ | ☐ | ||||

3.2. Runtime assignment[edit | edit source]

3.2.1. On STM32MP25x lines  [edit | edit source]

[edit | edit source]

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

Check boxes illustrate the possible peripheral allocations supported by STM32 MPU Embedded Software:

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in STM32 MPU Embedded Software distribution.

- ☐ means that the peripheral can be assigned to the given runtime context.

- ☑ means that the peripheral is assigned by default to the given runtime context and that the peripheral is mandatory for the STM32 MPU Embedded Software distribution.

- ✓ is used for system peripherals that cannot be unchecked because they are hardware connected in the device.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possibilities might be described in STM32MP25 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 non-secure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 non-secure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Analog | ADC | ADC12 | ⬚ | ☐ | ⬚ | ☐ | ||

| ADC3 | ⬚ | ☐ | ⬚ | ☑ | ADC3 may be used by the UCSI firmware to measure the Vbus level on the Type-C connector. | |||

4. Software frameworks and drivers[edit | edit source]

Below are listed the software frameworks and drivers managing the ADC peripheral for the embedded software components listed in the above tables.

- Linux®: IIO framework

- U-Boot: U-Boot ADC driver

5. How to assign and configure the peripheral[edit | edit source]

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral by generating:

- partial device trees (pin control and clock tree) for the OpenSTLinux software components,

- HAL initialization code for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.

For the Linux kernel U-boot and OP-TEE configuration, refer to ADC device tree configuration article.

6. How to go further[edit | edit source]

See application notes:

- How to get the best ADC accuracy in STM32[8].

7. References[edit | edit source]