Registered User mNo edit summary |

Registered User mNo edit summary Tag: 2017 source edit |

||

| (9 intermediate revisions by 2 users not shown) | |||

| Line 43: | Line 43: | ||

** Any processor can post asynchronously a message by setting the subchannel status flag to occupied. The "receiver" processor clears the flag when the message is treated. This mode can be considered as a combination of two simplex modes on a given channel. | ** Any processor can post asynchronously a message by setting the subchannel status flag to occupied. The "receiver" processor clears the flag when the message is treated. This mode can be considered as a combination of two simplex modes on a given channel. | ||

Refer to the [[STM32MP15 resources#Reference manuals|STM32MP15 reference manuals]] for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented. | Refer to the reference manuals<ref name="stm32mp157-Reference-manual">[[STM32MP15 resources#Reference manuals| STM32MP15 reference manuals]]</ref><ref name="stm32mp257-Reference-manual">[[STM32MP25 resources#Reference manuals| STM32MP25 reference manuals]]</ref> for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented. | ||

==Peripheral usage== | ==Peripheral usage== | ||

This chapter is applicable in the scope of the '''OpenSTLinux BSP''' running on the Arm<sup>®</sup> Cortex<sup>®</sup>-A processor(s), and the '''STM32CubeMPU Package''' running on the Arm<sup>®</sup> Cortex<sup>®</sup>-M processor. | This chapter is applicable in the scope of the '''OpenSTLinux BSP''' running on the Arm<sup>®</sup> Cortex<sup>®</sup>-A processor(s), and the '''STM32CubeMPU Package''' running on the Arm<sup>®</sup> Cortex<sup>®</sup>-M processor. | ||

===Processor interface assignment === | |||

====On {{MicroprocessorDevice | device=15}}==== | |||

STMicroelectronics distribution uses the IPCC peripheral for inter-processor communication with the following configuration: | |||

* The IPCC processor 1 interface (PROC1)is assigned to the Arm<sup>®</sup> Cortex<sup>®</sup>-A7, non-secure context. | |||

* The IPCC processor 2 interface (PROC2) is assigned to the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 context. | |||

====On {{MicroprocessorDevice | device=25}}==== | |||

* The IPCC1 peripheral is dedicated for the communication between the Arm<sup>®</sup> Cortex<sup>®</sup>-A35 and the Arm<sup>®</sup> Cortex<sup>®</sup>-M33. The interfaces are assigned in hardware to the Cortexes : | |||

** The processor 1 interface (PROC1) is assigned by hardware to the Arm<sup>®</sup> Cortex<sup>®</sup>-A35, secure and non-secure context. | |||

** The processor 2 interface (PROC2) is assigned by hardware to the Arm<sup>®</sup> Cortex<sup>®</sup>-M33, secure and non-secure context. | |||

* The IPCC2 peripheral is dedicated for the communication between the Arm<sup>®</sup> Cortex<sup>®</sup>-A35 or the Arm<sup>®</sup> Cortex<sup>®</sup>-M33 and the Arm<sup>®</sup> Cortex<sup>®</sup>-M0+. | |||

** The processor 1 interface (PROC1) is assigned by hardware to the Arm<sup>®</sup> Cortex<sup>®</sup>-M0+. | |||

** The processor 2 interface (PROC2) is assignable to the Arm<sup>®</sup> Cortex<sup>®</sup>-A35 or the Arm<sup>®</sup> Cortex<sup>®</sup>-M33, secure and non-secure context. | |||

===Boot time assignment=== | ===Boot time assignment=== | ||

====On {{MicroprocessorDevice | device= | ====On {{MicroprocessorDevice | device=15}}==== | ||

The IPCC peripheral is not used at boot time. | The IPCC peripheral is not used at boot time. | ||

====On {{MicroprocessorDevice | device= | ====On {{MicroprocessorDevice | device=25}}==== | ||

{{#lst:STM32MP2_internal_peripherals_assignment_table_template|stm32mp2_a35_boottime}} | {{#lst:STM32MP2_internal_peripherals_assignment_table_template|stm32mp2_a35_boottime}} | ||

<section begin=stm32mp25_a35_boottime /> | <section begin=stm32mp25_a35_boottime /> | ||

| Line 74: | Line 89: | ||

<span id="stm32mp2_IPCC1_a35_boottime_rif"></span>The below table shows the possible boot time allocations for the features of the '''IPCC1''' instance. | <span id="stm32mp2_IPCC1_a35_boottime_rif"></span>The below table shows the possible boot time allocations for the features of the '''IPCC1''' instance. | ||

{{#lst:STM32MP2_internal_peripherals_assignment_table_template|stm32mp2_a35_boottime_rif}} | {{#lst:STM32MP2_internal_peripherals_assignment_table_template|stm32mp2_a35_boottime_rif}} | ||

| | | PROC1 channel 1 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 80: | Line 95: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 2 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 86: | Line 101: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 3 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 92: | Line 107: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 4 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 98: | Line 113: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 5 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 104: | Line 119: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 6 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 110: | Line 125: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 7 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 116: | Line 131: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 8 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 122: | Line 137: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 9 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 128: | Line 143: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 10 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 134: | Line 149: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 11 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 140: | Line 155: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 12 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 146: | Line 161: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 13 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 152: | Line 167: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 14 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 158: | Line 173: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 15 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 164: | Line 179: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 16 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | | <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | ||

| Line 170: | Line 185: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 1 | ||

| | | | ||

| | | | ||

| Line 176: | Line 191: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 2 | ||

| | | | ||

| | | | ||

| Line 182: | Line 197: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 3 | ||

| | | | ||

| | | | ||

| Line 188: | Line 203: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 4 | ||

| | | | ||

| | | | ||

| Line 194: | Line 209: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 5 | ||

| | | | ||

| | | | ||

| Line 200: | Line 215: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 6 | ||

| | | | ||

| | | | ||

| Line 206: | Line 221: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 7 | ||

| | | | ||

| | | | ||

| Line 212: | Line 227: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 8 | ||

| | | | ||

| | | | ||

| Line 218: | Line 233: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 9 | ||

| | | | ||

| | | | ||

| Line 224: | Line 239: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 10 | ||

| | | | ||

| | | | ||

| Line 230: | Line 245: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 11 | ||

| | | | ||

| | | | ||

| Line 236: | Line 251: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 12 | ||

| | | | ||

| | | | ||

| Line 242: | Line 257: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 13 | ||

| | | | ||

| | | | ||

| Line 248: | Line 263: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 14 | ||

| | | | ||

| | | | ||

| Line 254: | Line 269: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 15 | ||

| | | | ||

| | | | ||

| Line 260: | Line 275: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 16 | ||

| | | | ||

| | | | ||

| Line 269: | Line 284: | ||

<br/> | <br/> | ||

<span id="stm32mp2_IPCC2_a35_boottime_rif"></span>The below table shows the possible boot time allocations for the features of the '''IPCC2''' instance. | <span id="stm32mp2_IPCC2_a35_boottime_rif"></span>The below table shows the possible boot time allocations for the features of the '''IPCC2''' instance. | ||

{{#lst:STM32MP2_internal_peripherals_assignment_table_template|stm32mp2_a35_boottime_rif}} | {{#lst:STM32MP2_internal_peripherals_assignment_table_template|stm32mp2_a35_boottime_rif}} | ||

| | | PROC1 channel 1 | ||

| | | | ||

| | | | ||

| | | | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 2 | ||

| | | | ||

| | | | ||

| | | | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 3 | ||

| | | | ||

| | | | ||

| Line 300: | Line 304: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 4 | ||

| | | | ||

| | | | ||

| Line 306: | Line 310: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 1 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | |||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | |||

| | | | ||

|- | |||

| PROC2 channel 2 | |||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | |||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | |||

| | | | ||

|- | |- | ||

| | | PROC2 channel 3 | ||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | |||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | |||

| | | | ||

|- | |||

| PROC2 channel 4 | |||

| | | | ||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | |||

| <span title="assignable peripheral but not supported" style="font-size:21px">⬚</span> | |||

| | | | ||

|- | |- | ||

| Line 321: | Line 337: | ||

===Runtime assignment=== | ===Runtime assignment=== | ||

It does not make sense to allocate the IPCC to a single runtime execution context. It is consequently enabled by default for both cores in the [[STM32CubeMX]]. | It does not make sense to allocate the IPCC to a single runtime execution context. It is consequently enabled by default for both cores in the [[STM32CubeMX]]. | ||

====On {{MicroprocessorDevice | device=15}}==== | |||

{{#lst:STM32MP1_internal_peripherals_assignment_table_template|stm32mp15_runtime}} | {{#lst:STM32MP1_internal_peripherals_assignment_table_template|stm32mp15_runtime}} | ||

<section begin=stm32mp15_runtime /> | <section begin=stm32mp15_runtime /> | ||

| Line 348: | Line 361: | ||

| style="color: white; background: {{STLightBlue}}; width:19%;" | '''Cortex-M4''' <br /> (STM32Cube) | | style="color: white; background: {{STLightBlue}}; width:19%;" | '''Cortex-M4''' <br /> (STM32Cube) | ||

|- | |- | ||

| | | PROC1 channel 1 | ||

| <span title="assigned peripheral" style="font-size:21px">☑ | | <span title="assigned peripheral" style="font-size:21px">☑ | ||

| | | | ||

| Line 356: | Line 369: | ||

* The Cortex-A core uses this channel to indicate that the message is treated | * The Cortex-A core uses this channel to indicate that the message is treated | ||

|- | |- | ||

| | | PROC1 channel 2 | ||

| <span title="assigned peripheral" style="font-size:21px">☑</span> | | <span title="assigned peripheral" style="font-size:21px">☑</span> | ||

| | | | ||

| Line 364: | Line 377: | ||

* The Cortex-M core uses this channel to indicate that the message is treated | * The Cortex-M core uses this channel to indicate that the message is treated | ||

|- | |- | ||

| | | PROC1 channel 3 | ||

| <span title="assigned peripheral" style="font-size:21px">☑</span> | | <span title="assigned peripheral" style="font-size:21px">☑</span> | ||

| | | | ||

| style="text-align: left;"|Simplex communication used by the [[Linux remoteproc framework overview |remote framework]] to request the Cortex-M4 to shutdown. | | style="text-align: left;"|Simplex communication used by the [[Linux remoteproc framework overview |remote framework]] to request the Cortex-M4 to shutdown. | ||

|- | |- | ||

| | | PROC1 channel 4 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| | | | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 5 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| | | | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 6 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| | | | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 1 | ||

| | | | ||

| <span title="assigned peripheral" style="font-size:21px">☑</span> | | <span title="assigned peripheral" style="font-size:21px">☑</span> | ||

| Line 392: | Line 405: | ||

* The Cortex-A core uses this channel to indicate that the message is treated | * The Cortex-A core uses this channel to indicate that the message is treated | ||

|- | |- | ||

| | | PROC2 channel 2 | ||

| | | | ||

| <span title="assigned peripheral" style="font-size:21px">☑</span> | | <span title="assigned peripheral" style="font-size:21px">☑</span> | ||

| Line 400: | Line 413: | ||

* The Cortex-M core uses this channel to indicate that the message is treated | * The Cortex-M core uses this channel to indicate that the message is treated | ||

|- | |- | ||

| | | PROC2 channel 3 | ||

| | | | ||

| <span title="assigned peripheral" style="font-size:21px">☑</span> | | <span title="assigned peripheral" style="font-size:21px">☑</span> | ||

| style="text-align: left;"|Simplex communication used by the [[Linux remoteproc framework overview |remote framework]] to request the Cortex-M4 to shutdown. | | style="text-align: left;"|Simplex communication used by the [[Linux remoteproc framework overview |remote framework]] to request the Cortex-M4 to shutdown. | ||

|- | |- | ||

| | | PROC2 channel 4 | ||

| | | | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 5 | ||

| | | | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 6 | ||

| | | | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 449: | Line 462: | ||

<span id="stm32mp25_IPCC1_a35_runtime_rif"></span>The below table shows the possible runtime allocations for the features of the '''IPCC1''' instance. | <span id="stm32mp25_IPCC1_a35_runtime_rif"></span>The below table shows the possible runtime allocations for the features of the '''IPCC1''' instance. | ||

{{#lst:STM32MP2_internal_peripherals_assignment_table_template|stm32mp25_runtime_rif}} | {{#lst:STM32MP2_internal_peripherals_assignment_table_template|stm32mp25_runtime_rif}} | ||

| | | PROC1 channel 1 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assigned peripheral" style="font-size:21px">☑</span> | | <span title="assigned peripheral" style="font-size:21px">☑</span> | ||

| Line 460: | Line 473: | ||

* The Cortex-A core uses this channel to indicate that the message is treated | * The Cortex-A core uses this channel to indicate that the message is treated | ||

|- | |- | ||

| | | PROC1 channel 2 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assigned peripheral" style="font-size:21px">☑</span> | | <span title="assigned peripheral" style="font-size:21px">☑</span> | ||

| Line 472: | Line 485: | ||

|- | |- | ||

| | | PROC1 channel 3 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assigned peripheral" style="font-size:21px">☑</span> | | <span title="assigned peripheral" style="font-size:21px">☑</span> | ||

| Line 480: | Line 493: | ||

| style="text-align: left;"|Simplex communication used by the [[Linux remoteproc framework overview | remoteproc framework]] to request the Cortex-M33 to shutdown. | | style="text-align: left;"|Simplex communication used by the [[Linux remoteproc framework overview | remoteproc framework]] to request the Cortex-M33 to shutdown. | ||

|- | |- | ||

| | | PROC1 channel 4 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 488: | Line 501: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 5 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 496: | Line 509: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 6 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 504: | Line 517: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 7 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 512: | Line 525: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 8 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 520: | Line 533: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 9 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 528: | Line 541: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 10 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 536: | Line 549: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 11 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 544: | Line 557: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 12 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 552: | Line 565: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 13 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 558: | Line 571: | ||

| | | | ||

| | | | ||

| | | style="text-align: left;"| Allocated to secure world but not used. | ||

|- | |- | ||

| | | PROC1 channel 14 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 566: | Line 579: | ||

| | | | ||

| | | | ||

| | | style="text-align: left;"| Allocated to secure world but not used. | ||

|- | |- | ||

| | | PROC1 channel 15 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 574: | Line 587: | ||

| | | | ||

| | | | ||

| | | style="text-align: left;"| Allocated to secure world but not used. | ||

|- | |- | ||

| | | PROC1 channel 16 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | | <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| Line 582: | Line 595: | ||

| | | | ||

| | | | ||

| | | style="text-align: left;"| Allocated to secure world but not used. {{ReviewsComments | [[User:Valentin Caron|Valentin Caron]] ([[User talk:Valentin Caron|talk]]) 15:29, 11 June 2024 (CEST) - Should become "Used by [[SCMI overview|SCMI]]." and affected to OP-TEE for v6.0}} | ||

|- | |- | ||

| | | PROC2 channel 1 | ||

| | | | ||

| | | | ||

| Line 595: | Line 608: | ||

* The Cortex-A core uses this channel to indicate that the message is treated | * The Cortex-A core uses this channel to indicate that the message is treated | ||

|- | |- | ||

| | | PROC2 channel 2 | ||

| | | | ||

| | | | ||

| Line 607: | Line 620: | ||

|- | |- | ||

| | | PROC2 channel 3 | ||

| | | | ||

| | | | ||

| Line 615: | Line 628: | ||

| style="text-align: left;"|Simplex communication used by the [[Linux remoteproc framework overview| remoteproc framework]] to request the Cortex-M33 to shutdown. | | style="text-align: left;"|Simplex communication used by the [[Linux remoteproc framework overview| remoteproc framework]] to request the Cortex-M33 to shutdown. | ||

|- | |- | ||

| | | PROC2 channel 4 | ||

| | | | ||

| | | | ||

| Line 623: | Line 636: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 5 | ||

| | | | ||

| | | | ||

| Line 631: | Line 644: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 6 | ||

| | | | ||

| | | | ||

| Line 639: | Line 652: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 7 | ||

| | | | ||

| | | | ||

| Line 647: | Line 660: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 8 | ||

| | | | ||

| | | | ||

| Line 655: | Line 668: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 9 | ||

| | | | ||

| | | | ||

| Line 663: | Line 676: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 10 | ||

| | | | ||

| | | | ||

| Line 671: | Line 684: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 11 | ||

| | | | ||

| | | | ||

| Line 679: | Line 692: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 12 | ||

| | | | ||

| | | | ||

| Line 687: | Line 700: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 13 | ||

| | | | ||

| | | | ||

| Line 695: | Line 708: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 14 | ||

| | | | ||

| | | | ||

| Line 703: | Line 716: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 15 | ||

| | | | ||

| | | | ||

| Line 711: | Line 724: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 16 | ||

| | | | ||

| | | | ||

| Line 717: | Line 730: | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| | | | ||

| | | {{ReviewsComments | [[User:Valentin Caron|Valentin Caron]] ([[User talk:Valentin Caron|talk]]) 15:29, 11 June 2024 (CEST) - Should become "Used by [[SCMI overview|SCMI]]." and affected to M33 Cube for v6.0}} | ||

|- | |- | ||

|} | |} | ||

| Line 723: | Line 736: | ||

<span id="stm32mp25_IPCC2_a35_runtime_rif"></span>The below table shows the possible runtime allocations for the features of the '''IPCC2''' instance. | <span id="stm32mp25_IPCC2_a35_runtime_rif"></span>The below table shows the possible runtime allocations for the features of the '''IPCC2''' instance. | ||

{{#lst:STM32MP2_internal_peripherals_assignment_table_template|stm32mp25_runtime_rif}} | {{#lst:STM32MP2_internal_peripherals_assignment_table_template|stm32mp25_runtime_rif}} | ||

| | | PROC1 channel 1 | ||

| | | | ||

| | | | ||

| | | | ||

| | | | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 2 | ||

| | | | ||

| | | | ||

| Line 763: | Line 752: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 3 | ||

| | | | ||

| | | | ||

| Line 771: | Line 760: | ||

| | | | ||

|- | |- | ||

| | | PROC1 channel 4 | ||

| | | | ||

| | | | ||

| Line 779: | Line 768: | ||

| | | | ||

|- | |- | ||

| | | PROC2 channel 1 | ||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| | |||

| | |||

|- | |||

| PROC2 channel 2 | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| | | | ||

| | | | ||

|- | |||

| PROC2 channel 3 | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| | | | ||

| | | | ||

|- | |||

| PROC2 channel 4 | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span><sup>OP-TEE</sup> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | |||

| <span title="assignable peripheral" style="font-size:21px">☐</span> | | <span title="assignable peripheral" style="font-size:21px">☐</span> | ||

| | |||

| | | | ||

|- | |- | ||

|} | |} | ||

Latest revision as of 08:48, 24 July 2024

1. Article purpose

The purpose of this article is to:

- briefly introduce the IPCC peripheral and its main features,

- indicate the peripheral instances assignment at boot time and their assignment at runtime (including whether instances can be allocated to secure contexts),

- list the software frameworks and drivers managing the peripheral,

- explain how to configure the peripheral.

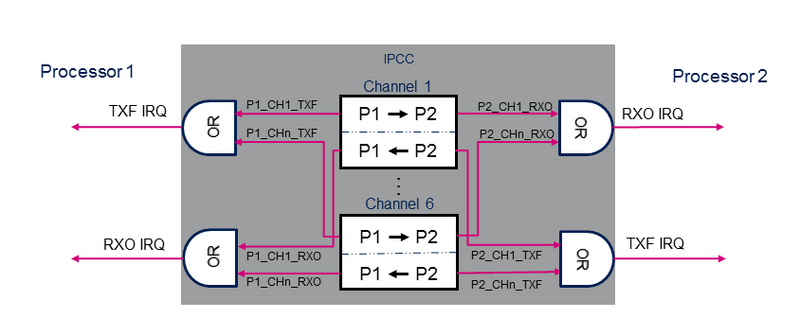

2. Peripheral overview

The IPCC (inter-processor communication controller) peripheral is used to exchange data between two processors. It provides a non blocking signaling mechanism to post and retrieve information in an atomic way. Note that shared memory buffers are allocated in the MCU SRAM, which is not part of the IPCC block.

The IPCC peripheral provides a hardware support to manage inter-processor communication between two processor instances. Each processor owns specific register bank and interrupts.

The IPCC provides the signaling for six bidirectional channels.

Each channel is divided into two subchannels that offer a unidirectional signaling from the "sender" processor to the "receiver" processor:

- P1_TO_P2 subchannel

- P2_TO_P1 subchannel

A subchannel consists in:

- One flag that toggles between occupied and free: the flag is set to occupied by the "sender" processor and cleared by the "receiver" processor.

- Two associated interrupts (shared with the other channels):

- RXO: RX channel occupied, connected to the "receiver" processor.

- TXF: TX channel free, connected to the "sender" processor.

- Two associated interrupt masks multiplexing channel IRQs.

The IPCC supports the following channel operating modes:

- Simplex communication mode:

- Only one subchannel is used.

- Unidirectional messages: once the "sender" processor has posted the communication data in the memory, it sets the channel status flag to occupied. The "receiver" processor clears the flag when the message is treated.

- Half-duplex communication mode:

- Only one subchannel is used.

- Bidirectional messages: once the "sender" processor has posted the communication data in the memory, it sets the channel status flag to occupied. The "receiver" processor clears the flag when the message is treated and the response is available in shared memory.

- Full-duplex communication mode:

- The subchannels are used in Asynchronous mode.

- Any processor can post asynchronously a message by setting the subchannel status flag to occupied. The "receiver" processor clears the flag when the message is treated. This mode can be considered as a combination of two simplex modes on a given channel.

Refer to the reference manuals[1][2] for the complete list of features, and to the software frameworks and drivers, introduced below, to see which features are implemented.

3. Peripheral usage

This chapter is applicable in the scope of the OpenSTLinux BSP running on the Arm® Cortex®-A processor(s), and the STM32CubeMPU Package running on the Arm® Cortex®-M processor.

3.1. Processor interface assignment

3.1.1. On STM32MP15x lines

STMicroelectronics distribution uses the IPCC peripheral for inter-processor communication with the following configuration:

- The IPCC processor 1 interface (PROC1)is assigned to the Arm® Cortex®-A7, non-secure context.

- The IPCC processor 2 interface (PROC2) is assigned to the Arm® Cortex®-M4 context.

3.1.2. On STM32MP25x lines

- The IPCC1 peripheral is dedicated for the communication between the Arm® Cortex®-A35 and the Arm® Cortex®-M33. The interfaces are assigned in hardware to the Cortexes :

- The processor 1 interface (PROC1) is assigned by hardware to the Arm® Cortex®-A35, secure and non-secure context.

- The processor 2 interface (PROC2) is assigned by hardware to the Arm® Cortex®-M33, secure and non-secure context.

- The IPCC2 peripheral is dedicated for the communication between the Arm® Cortex®-A35 or the Arm® Cortex®-M33 and the Arm® Cortex®-M0+.

- The processor 1 interface (PROC1) is assigned by hardware to the Arm® Cortex®-M0+.

- The processor 2 interface (PROC2) is assignable to the Arm® Cortex®-A35 or the Arm® Cortex®-M33, secure and non-secure context.

3.2. Boot time assignment

3.2.1. On STM32MP15x lines

The IPCC peripheral is not used at boot time.

3.2.2. On STM32MP25x lines

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Boot time allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 non-secure (U-Boot) | |||

| Coprocessor | IPCC |

IPCC1 | ⬚ | ⬚ | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | |

| IPCC2 | ⬚ | ⬚ | Shareable at internal peripheral level thanks to the RIF: see the boot time allocation per feature | |||

The below table shows the possible boot time allocations for the features of the IPCC1 instance.

| Feature | Boot time allocation |

Comment | ||

|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 non-secure (U-Boot) | ||

| PROC1 channel 1 | ⬚ | ⬚ | ||

| PROC1 channel 2 | ⬚ | ⬚ | ||

| PROC1 channel 3 | ⬚ | ⬚ | ||

| PROC1 channel 4 | ⬚ | ⬚ | ||

| PROC1 channel 5 | ⬚ | ⬚ | ||

| PROC1 channel 6 | ⬚ | ⬚ | ||

| PROC1 channel 7 | ⬚ | ⬚ | ||

| PROC1 channel 8 | ⬚ | ⬚ | ||

| PROC1 channel 9 | ⬚ | ⬚ | ||

| PROC1 channel 10 | ⬚ | ⬚ | ||

| PROC1 channel 11 | ⬚ | ⬚ | ||

| PROC1 channel 12 | ⬚ | ⬚ | ||

| PROC1 channel 13 | ⬚ | ⬚ | ||

| PROC1 channel 14 | ⬚ | ⬚ | ||

| PROC1 channel 15 | ⬚ | ⬚ | ||

| PROC1 channel 16 | ⬚ | ⬚ | ||

| PROC2 channel 1 | ||||

| PROC2 channel 2 | ||||

| PROC2 channel 3 | ||||

| PROC2 channel 4 | ||||

| PROC2 channel 5 | ||||

| PROC2 channel 6 | ||||

| PROC2 channel 7 | ||||

| PROC2 channel 8 | ||||

| PROC2 channel 9 | ||||

| PROC2 channel 10 | ||||

| PROC2 channel 11 | ||||

| PROC2 channel 12 | ||||

| PROC2 channel 13 | ||||

| PROC2 channel 14 | ||||

| PROC2 channel 15 | ||||

| PROC2 channel 16 | ||||

The below table shows the possible boot time allocations for the features of the IPCC2 instance.

| Feature | Boot time allocation |

Comment | ||

|---|---|---|---|---|

| Cortex-A35 secure (ROM code) |

Cortex-A35 secure (TF-A BL2) |

Cortex-A35 non-secure (U-Boot) | ||

| PROC1 channel 1 | ||||

| PROC1 channel 2 | ||||

| PROC1 channel 3 | ||||

| PROC1 channel 4 | ||||

| PROC2 channel 1 | ⬚ | ⬚ | ||

| PROC2 channel 2 | ⬚ | ⬚ | ||

| PROC2 channel 3 | ⬚ | ⬚ | ||

| PROC2 channel 4 | ⬚ | ⬚ | ||

3.3. Runtime assignment

It does not make sense to allocate the IPCC to a single runtime execution context. It is consequently enabled by default for both cores in the STM32CubeMX.

3.3.1. On STM32MP15x lines

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Coprocessor | IPCC | IPCC | ☑ | ☑ | Shared (none or both) | |

| Processor interface | Context | Comment | ||

|---|---|---|---|---|

| Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| PROC1 channel 1 | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| ||

| PROC1 channel 2 | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| ||

| PROC1 channel 3 | ☑ | Simplex communication used by the remote framework to request the Cortex-M4 to shutdown. | ||

| PROC1 channel 4 | ☐ | |||

| PROC1 channel 5 | ☐ | |||

| PROC1 channel 6 | ☐ | |||

| PROC2 channel 1 | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| ||

| PROC2 channel 2 | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| ||

| PROC2 channel 3 | ☑ | Simplex communication used by the remote framework to request the Cortex-M4 to shutdown. | ||

| PROC2 channel 4 | ☐ | |||

| PROC2 channel 5 | ☐ | |||

| PROC2 channel 6 | ☐ | |||

3.3.2. On STM32MP25x lines

Click on ![]() to expand or collapse the legend...

to expand or collapse the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||||

|---|---|---|---|---|---|---|---|---|

| Instance | Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 non-secure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 non-secure (STM32Cube) |

Cortex-M0+ (STM32Cube) | |||

| Coprocessor | IPCC |

IPCC1 | ☐OP-TEE | ☐ | ☐ | ☐ | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | |

| IPCC2 | ☐OP-TEE | ☐ | ☐ | ☐ | ☐ | Shareable at internal peripheral level thanks to the RIF: see the runtime allocation per feature | ||

The below table shows the possible runtime allocations for the features of the IPCC1 instance.

| Feature | Runtime allocation |

Comment | ||||

|---|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 non-secure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 non-secure (STM32Cube) |

Cortex-M0+ (STM32Cube) | ||

| PROC1 channel 1 | ☐OP-TEE | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| |||

| PROC1 channel 2 | ☐OP-TEE | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| |||

| PROC1 channel 3 | ☐OP-TEE | ☑ | Simplex communication used by the remoteproc framework to request the Cortex-M33 to shutdown. | |||

| PROC1 channel 4 | ☐OP-TEE | ☐ | ||||

| PROC1 channel 5 | ☐OP-TEE | ☐ | ||||

| PROC1 channel 6 | ☐OP-TEE | ☐ | ||||

| PROC1 channel 7 | ☐OP-TEE | ☐ | ||||

| PROC1 channel 8 | ☐OP-TEE | ☐ | ||||

| PROC1 channel 9 | ☐OP-TEE | ☐ | ||||

| PROC1 channel 10 | ☐OP-TEE | ☐ | ||||

| PROC1 channel 11 | ☐OP-TEE | ☐ | ||||

| PROC1 channel 12 | ☐OP-TEE | ☐ | ||||

| PROC1 channel 13 | ☐OP-TEE | ☐ | Allocated to secure world but not used. | |||

| PROC1 channel 14 | ☐OP-TEE | ☐ | Allocated to secure world but not used. | |||

| PROC1 channel 15 | ☐OP-TEE | ☐ | Allocated to secure world but not used. | |||

| PROC1 channel 16 | ☐OP-TEE | ☐ | Allocated to secure world but not used. | |||

| PROC2 channel 1 | ☐ | ☑ | RPMsg transfer from Cortex-M to Cortex-A

Full-duplex communication:

| |||

| PROC2 channel 2 | ☐ | ☑ | RPMsg transfer from Cortex-A to Cortex-M

Full-duplex communication:

| |||

| PROC2 channel 3 | ☐ | ☑ | Simplex communication used by the remoteproc framework to request the Cortex-M33 to shutdown. | |||

| PROC2 channel 4 | ☐ | ☐ | ||||

| PROC2 channel 5 | ☐ | ☐ | ||||

| PROC2 channel 6 | ☐ | ☐ | ||||

| PROC2 channel 7 | ☐ | ☐ | ||||

| PROC2 channel 8 | ☐ | ☐ | ||||

| PROC2 channel 9 | ☐ | ☐ | ||||

| PROC2 channel 10 | ☐ | ☐ | ||||

| PROC2 channel 11 | ☐ | ☐ | ||||

| PROC2 channel 12 | ☐ | ☐ | ||||

| PROC2 channel 13 | ☐ | ☐ | ||||

| PROC2 channel 14 | ☐ | ☐ | ||||

| PROC2 channel 15 | ☐ | ☐ | ||||

| PROC2 channel 16 | ☐ | ☐ | ||||

The below table shows the possible runtime allocations for the features of the IPCC2 instance.

| Feature | Runtime allocation |

Comment | ||||

|---|---|---|---|---|---|---|

| Cortex-A35 secure (OP-TEE / TF-A BL31) |

Cortex-A35 non-secure (Linux) |

Cortex-M33 secure (TF-M) |

Cortex-M33 non-secure (STM32Cube) |

Cortex-M0+ (STM32Cube) | ||

| PROC1 channel 1 | ☐ | |||||

| PROC1 channel 2 | ☐ | |||||

| PROC1 channel 3 | ☐ | |||||

| PROC1 channel 4 | ☐ | |||||

| PROC2 channel 1 | ☐OP-TEE | ☐ | ☐ | ☐ | ||

| PROC2 channel 2 | ☐OP-TEE | ☐ | ☐ | ☐ | ||

| PROC2 channel 3 | ☐OP-TEE | ☐ | ☐ | ☐ | ||

| PROC2 channel 4 | ☐OP-TEE | ☐ | ☐ | ☐ | ||

4. Software frameworks and drivers

Below are listed the software frameworks and drivers managing the IPCC peripheral for the embedded software components listed in the above tables.

- Linux®: mailbox framework

- STM32Cube: IPCC HAL driver and header file of IPCC HAL module

5. How to assign and configure the peripheral

The peripheral assignment can be done via the STM32CubeMX graphical tool (and manually completed if needed).

This tool also helps to configure the peripheral:

- partial device trees (pin control and clock tree) generation for the OpenSTLinux software components,

- HAL initialization code generation for the STM32CubeMPU Package.

The configuration is applied by the firmware running in the context in which the peripheral is assigned.The IPCC peripheral is shared between the Arm Cortex-A and Cortex-M contexts. A particular attention must therefore be paid to have a complementary configuration on both contexts.