1. Article purpose[edit source]

The purpose of this article is to:

- briefly introduce the PWR peripheral and its main features

- indicate the level of security supported by this hardware block

- explain how it can be allocated to the three runtime contexts and linked to the corresponding software components

- explain, when necessary, how to configure the PWR peripheral.

2. Peripheral overview[edit source]

The PWR peripheral is used to control the device power supply configuration.

It has 6 input pins (named wakeup pins) which can be programmed to wake the system up from low power. The wakeup pins are listed with WKUP prefix in the STM32MP13 Datasheet.

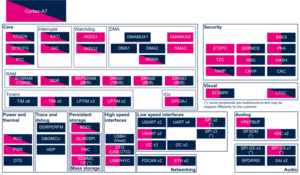

These pins can be used by the Cortex®-A7 non secure (via Cortex®-A7 secure services).

The PWR peripheral provides 3 output hardware lines named PWR_ON, PWR_LP and PWR_CPU_ON:

- In STPMIC1 configuration, PWR_ON allows to select the register bank (active or low power). PWR_LP and PWR_CPU_ON are not used.

- In the power discrete solution they drive VDDcore which feeds the Cortex®-A7 and the peripherals. They also control the DDR power supplies (VDD_DDR, VREF_DDR, VTT_DDR) and VDDCpu that feeds the porcessor.

2.1. Features[edit source]

Refer to the STM32MP13 reference manuals for the complete list of features, and to the software components, introduced below, to see which features are implemented.

2.2. Security support[edit source]

The PWR is secure aware with the security control managed via RCC TZEN bit.

3. Peripheral usage and associated software[edit source]

3.1. Boot time[edit source]

The PWR is closely configured together with RCC by all the boot components: the ROM code, the FSBL, the SSBL and up to Linux® kernel. Its configuration is carried by the device tree.

3.2. Runtime[edit source]

3.2.1. Overview[edit source]

The PWR peripheral is not shared at runtime:

- the Cortex®-A7 secure controls all secure registers (cf. TZEN description above) with PWR OP-TEE driver.

3.2.2. Software frameworks[edit source]

| Domain | Peripheral | Software components | Comment | |

|---|---|---|---|---|

| OP-TEE | Linux | |||

| Power & Thermal | PWR | OP-TEE PWR driver | ||

3.2.3. Peripheral configuration[edit source]

The configuration is applied by the firmware running in the context to which the peripheral is assigned. The configuration can be done alone via the STM32CubeMX tool for all internal peripherals, and then manually completed (particularly for external peripherals), according to the information given in the corresponding software framework article.

3.2.4. Peripheral assignment[edit source]

Click on the right to expand the legend...

Check boxes illustrate the possible peripheral allocations supported by STM32 MPU Embedded Software:

- ☐ means that the peripheral can be assigned (☑) to the given runtime context.

- ⬚ means that the peripheral can be assigned to the given runtime context, but this configuration is not supported in STM32 MPU Embedded Software distribution.

- ✓ is used for system peripherals that cannot be unchecked because they are statically connected in the device.

Refer to How to assign an internal peripheral to a runtime context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possiblities might be described in STM32MP13 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) | |||

| Power & Thermal | PWR | PWR | ✓ | ||

4. How to go further[edit source]

The PWR is interfaced with the hardware debug port (HDP) of the STM32MP13. This link offers the flexibility to observe the main PWR state signals on debug pins.

Please refer to STM32MP13 reference manuals for the exact list of signals that can be monitored.

5. References[edit source]