1. Article purpose[edit source]

The purpose of this article is to

- briefly introduce the OTG peripheral and its main features

- indicate the level of security supported by this hardware block

- explain how it can be allocated to the runtime contexts and linked to the corresponding software components

- explain, when needed, how to configure the OTG peripheral.

2. Peripheral overview[edit source]

The OTG peripheral is used to interconnect other systems with STM32 MPU devices, using USB standard.

2.1. Features[edit source]

The OTG peripheral is a USB Dual-Role Device (DRD) controller that supports both device and host functions.

| OTG speeds supported | HS (480 Mb/s) | FS (12 Mb/s) | LS (1.5 Mb/s) |

|---|---|---|---|

| Host mode | |||

| Device mode |

OTG supports the following PHY interfaces:

| OTG peripheral PHY interfaces | STM32MP13x lines |

STM32MP15x lines |

|---|---|---|

| UTMI interface connected to internal HS PHY for HS/FS/LS speeds | ||

| On-chip full-speed PHY for FS/LS speeds |

The OTG peripheral is fully compliant with

- On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification[1], Revision 2.0, May 8, 2009

- Universal Serial Bus Revision 2.0 Specification[2], Revision 2.0, April 27, 2000

- USB 2.0 Link Power Management Addendum Engineering Change Notice to the USB 2.0 specification[3], July 16, 2007

- USB 2.0 Transceiver Macrocell Interface (UTMI) Specification[4], Version 1.05, March 29, 2001

- UTMI+ Specification[5], Revision 1.0, February 25, 2004

Refer to STM32MP13 reference manuals or STM32MP15 reference manuals for the complete hardware feature list, and to the software components (introduced below) to know which features are supported.

2.2. Security support[edit source]

2.2.1. On STM32MP13x lines  [edit source]

[edit source]

The OTG is a secure programmable peripheral (under ETZPC control).

2.2.2. On STM32MP15x lines  [edit source]

[edit source]

The OTG peripheral is a non-secure peripheral.

3. Peripheral usage and associated software[edit source]

3.1. Boot time[edit source]

The OTG peripheral is used by ROM code, FSBL and SSBL in device mode (DFU) to support serial boot for flash programming with STM32CubeProgrammer.

3.2. Runtime[edit source]

3.2.1. Overview[edit source]

The OTG peripheral can be allocated to the Arm® Cortex®-A7 non-secure core to be used under Linux® with USB framework.

On STM32MP13x lines ![]() only, the OTG peripheral can be allocated to the Arm® Cortex®-A7 secure context but this is not supported in OpenSTLinux.

only, the OTG peripheral can be allocated to the Arm® Cortex®-A7 secure context but this is not supported in OpenSTLinux.

3.2.2. Software frameworks[edit source]

3.2.2.1. On STM32MP13x lines  [edit source]

[edit source]

| Domain | Peripheral | Software components | Comment | |

|---|---|---|---|---|

| OP-TEE | Linux | |||

| High speed interface | OTG (USB OTG) | Linux USB framework | ||

3.2.2.2. On STM32MP15x lines  [edit source]

[edit source]

| Domain | Peripheral | Software components | Comment | ||

|---|---|---|---|---|---|

| OP-TEE | Linux | STM32Cube | |||

| High speed interface | OTG (USB OTG) | Linux USB framework | |||

3.2.3. Peripheral configuration[edit source]

The configuration is applied by the firmware running in the context to which the peripheral is assigned. The configuration by itself can be performed via the STM32CubeMX tool for all internal peripherals. It can then be manually completed (especially for external peripherals) according to the information given in the corresponding software framework article.

For Linux kernel configuration, please refer to OTG device tree configuration.

For U-boot configuration, please refer to Configure USB OTG node in U-Boot.

3.2.4. Peripheral assignment[edit source]

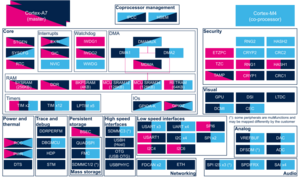

3.2.4.1. On STM32MP13x lines  [edit source]

[edit source]

Click on the right to expand the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) | |||

| High speed interface | OTG (USB OTG) | OTG (USB OTG) | ⬚ | ☐ | Assignment (single choice) |

3.2.4.2. On STM32MP15x lines  [edit source]

[edit source]

Click on the right to expand the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| High speed interface | OTG (USB OTG) | OTG (USB OTG) | ☐ | |||

4. References[edit source]