Registered User (add some information about OTP access conditions) |

Registered User mNo edit summary |

||

| (12 intermediate revisions by 6 users not shown) | |||

| Line 1: | Line 1: | ||

<noinclude>{{ApplicableFor | |||

|MPUs list=STM32MP13x, STM32MP15x | |||

|MPUs checklist=STM32MP13x,STM32MP15x | |||

}}</noinclude> | |||

==Article purpose== | ==Article purpose== | ||

The purpose of this article is to | The purpose of this article is to | ||

* briefly introduce the BSEC peripheral and its main features | * briefly introduce the BSEC peripheral and its main features | ||

* indicate the level of security supported by this hardware block | * indicate the level of security supported by this hardware block | ||

* explain how each instance can be allocated to the | * explain how each instance can be allocated to the runtime contexts and linked to the corresponding software components | ||

* explain, when necessary, how to configure the BSEC peripheral. | * explain, when necessary, how to configure the BSEC peripheral. | ||

| Line 10: | Line 14: | ||

===Features=== | ===Features=== | ||

Refer to [[STM32MP15 resources#Reference manuals|STM32MP15 reference manuals]] for the complete list of features, and to the software components, introduced below, to see which features are implemented.<br> | Refer to [[STM32MP13 resources#Reference manuals|STM32MP13 reference manuals]] or [[STM32MP15 resources#Reference manuals|STM32MP15 reference manuals]] for the complete list of features, and to the software components, introduced below, to see which features are implemented.<br> | ||

===Security support=== | ===Security support=== | ||

| Line 22: | Line 26: | ||

====Overview==== | ====Overview==== | ||

The BSEC | The BSEC is a system peripheral and is controlled by the Arm<sup>®</sup> Cortex<sup>®</sup>-A7 secure: | ||

{{Info| | {{Info| | ||

* BSEC lower OTP access can be made available to the Arm<sup>®</sup> Cortex<sup>®</sup>-A7 non-secure. | |||

* Upper OTP access can be managed as exceptions: | |||

:* on {{MicroprocessorDevice | device=13}}, using [[OP-TEE_overview|OP-TEE]] PTA | |||

:* on {{MicroprocessorDevice | device=15}}, using [[TF-A overview|TF-A]] "secure monitor calls" or [[OP-TEE_overview|OP-TEE]] PTA | |||

Please refer to [[BSEC device tree configuration]] for more details.}} | |||

====Software frameworks==== | ====Software frameworks==== | ||

{{: | ===== On {{MicroprocessorDevice | device=13}} ===== | ||

{{:STM32MP13 internal peripherals software table template}} | |||

| Security | | Security | ||

| [[BSEC internal peripheral|BSEC]] | | [[BSEC internal peripheral|BSEC]] | ||

| [[OP- | | [[OP-TEE_OTP_overview|OP-TEE OTP PTA ]] | ||

| [[NVMEM_overview|Linux NVMEM framework]] | |||

| | |||

|- | |||

|} | |||

===== On {{MicroprocessorDevice | device=15}} ===== | |||

{{:STM32MP15_internal_peripherals_software_table_template}} | |||

| Security | |||

| [[BSEC internal peripheral|BSEC]] | |||

| [[OP-TEE_OTP_overview|OP-TEE OTP PTA]] | |||

| [[NVMEM_overview|Linux NVMEM framework]] | | [[NVMEM_overview|Linux NVMEM framework]] | ||

| | | | ||

| Line 45: | Line 62: | ||

====Peripheral assignment==== | ====Peripheral assignment==== | ||

{{: | ===== On {{MicroprocessorDevice | device=13}} ===== | ||

< | {{:STM32MP13_internal_peripherals_assignment_table_template}} | ||

<section begin=stm32mp13 /> | |||

| rowspan="1" | Security | |||

| rowspan="1" | [[BSEC internal peripheral|BSEC]] | |||

| BSEC | |||

| <span title="system peripheral" style="font-size:21px">✓</span> | |||

| <span title="system peripheral" style="font-size:21px">✓</span> | |||

| | |||

|- | |||

<section end=stm32mp13 /> | |||

|} | |||

===== On {{MicroprocessorDevice | device=15}} ===== | |||

{{:STM32MP15_internal_peripherals_assignment_table_template}} | |||

<section begin=stm32mp15 /> | |||

| rowspan="1" | Security | | rowspan="1" | Security | ||

| rowspan="1" | [[BSEC internal peripheral|BSEC]] | | rowspan="1" | [[BSEC internal peripheral|BSEC]] | ||

| Line 55: | Line 85: | ||

| | | | ||

|- | |- | ||

</ | <section end=stm32mp15 /> | ||

|} | |} | ||

| Line 65: | Line 95: | ||

<noinclude> | <noinclude> | ||

[[Category:Persistent storage peripherals]] | [[Category:Persistent storage peripherals]] | ||

{{ArticleBasedOnModel| | {{ArticleBasedOnModel| Internal_peripheral_article_model}} | ||

{{PublicationRequestId | 8892 (PhilipS) | 2018-10-17}} | {{PublicationRequestId | 8892 (PhilipS) | 2018-10-17}} | ||

</noinclude> | </noinclude> | ||

Latest revision as of 17:03, 10 March 2023

1. Article purpose

The purpose of this article is to

- briefly introduce the BSEC peripheral and its main features

- indicate the level of security supported by this hardware block

- explain how each instance can be allocated to the runtime contexts and linked to the corresponding software components

- explain, when necessary, how to configure the BSEC peripheral.

2. Peripheral overview

The BSEC peripheral is used to control an OTP (one time programmable) fuse box, used for on-chip non-volatile storage for device configuration and security parameters.

2.1. Features

Refer to STM32MP13 reference manuals or STM32MP15 reference manuals for the complete list of features, and to the software components, introduced below, to see which features are implemented.

2.2. Security support

The BSEC is a secure peripheral.

3. Peripheral usage and associated software

3.1. Boot time

The BSEC is configured at boot time to set up platform security.

3.2. Runtime

3.2.1. Overview

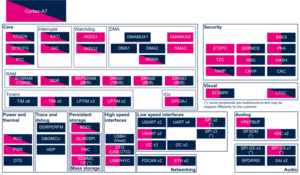

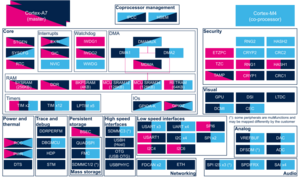

The BSEC is a system peripheral and is controlled by the Arm® Cortex®-A7 secure:

3.2.2. Software frameworks

3.2.2.1. On STM32MP13x lines

| Domain | Peripheral | Software components | Comment | |

|---|---|---|---|---|

| OP-TEE | Linux | |||

| Security | BSEC | OP-TEE OTP PTA | Linux NVMEM framework | |

3.2.2.2. On STM32MP15x lines

| Domain | Peripheral | Software components | Comment | ||

|---|---|---|---|---|---|

| OP-TEE | Linux | STM32Cube | |||

| Security | BSEC | OP-TEE OTP PTA | Linux NVMEM framework | ||

3.2.3. Peripheral configuration

The configuration is based on Device tree, please refer to BSEC device tree configuration article.

It can be applied by the firmware running in a secure context, done in TF-A or in OP-TEE.

It can also be configured by Linux® kernel, please refer to NVMEM overview article.

3.2.4. Peripheral assignment

3.2.4.1. On STM32MP13x lines

Click on the right to expand the legend...

| Domain | Peripheral | Runtime allocation | Comment | ||

|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) | |||

| Security | BSEC | BSEC | ✓ | ✓ | |

3.2.4.2. On STM32MP15x lines

Click on the right to expand the legend...

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Security | BSEC | BSEC | ✓ | ✓ | ||

4. How to go further

5. References