Registered User mNo edit summary |

Registered User mNo edit summary |

||

| (23 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

In a first part, this article shows the STM32MP157 line '''part number codification''' and '''block diagram'''. STM32MP157 belongs to STM32MP1 Series (refer to the list of part numbers provided below).<br><br> | |||

< | |||

The second part of this article digs into technical aspects, and provides entry points to: | The second part of this article digs into technical aspects, and provides entry points to: | ||

* STM32MP15 '''documentation''' | * STM32MP15 '''documentation''' | ||

| Line 16: | Line 6: | ||

* the list of '''boards''' supporting STM32MP15 devices | * the list of '''boards''' supporting STM32MP15 devices | ||

* the supported '''software distributions''', that can be dowloaded into the STM32MP15 device. | * the supported '''software distributions''', that can be dowloaded into the STM32MP15 device. | ||

==Introduction == | ==Introduction == | ||

| Line 23: | Line 12: | ||

Arm<sup>®</sup> Cortex<sup>®</sup>-M4 coprocessor and its peripheral set are directly inherited from the STM32 MCU family <ref>[http://www.st.com/en/microcontrollers/stm32-32-bit-arm-cortex-mcus.html STM32 MCU family]</ref>. | Arm<sup>®</sup> Cortex<sup>®</sup>-M4 coprocessor and its peripheral set are directly inherited from the STM32 MCU family <ref>[http://www.st.com/en/microcontrollers/stm32-32-bit-arm-cortex-mcus.html STM32 MCU family]</ref>. | ||

==Part number codification == | ==Part number codification == | ||

The table below shows the STM32MP15 microprocessor different part numbers available, together with their corresponding internal peripherals, security options and packages.<br /> | The table below shows the STM32MP15 microprocessor different part numbers available, together with their corresponding internal peripherals, security options and packages.<br /> | ||

=== STM32MP15x lines === | |||

:{| class=" | :{| class="st-table" | ||

|- | |- | ||

! !! | ! !! style="text-align:center;" | Cortex-A7 !! style="text-align:center;" | Cortex-M4 !! style="text-align:center;" | GPU !! style="text-align:center;" | Display !! style="text-align:center;" | CAN | ||

|- | |- | ||

| | | STM32MP15'''1''' || Single || Yes || No || TFT || No | ||

|- | |- | ||

| | | STM32MP15'''3''' || Dual || Yes || No || TFT || Yes | ||

|- | |- | ||

| | | STM32MP15'''7''' || Dual || Yes || Yes || TFT/DSI || Yes | ||

|} | |||

=== Security and Cortex-A7 frequency=== | |||

:{| class="st-table" | |||

! !! style="text-align:center;" | Security !! style="text-align:center;" | Cortex-A7 frequency | |||

|- | |- | ||

| | | STM32MP15x'''A''' || Basic || 650 MHz<ref name="mission profile">Exposure to maximum rating conditions for | ||

extended periods may affect device reliability. Device mission profile (application conditions) | |||

is compliant with JEDEC JESD47 qualification standard. Refer to the [[STM32MP15 resources#DS12505|STM32MP15 Datasheet]] and [[STM32MP15 resources#AN5438|AN5438]] for further information.</ref> | |||

|- | |- | ||

| | | STM32MP15x'''C''' || Secure boot + Cryptography ([[CRYP internal peripheral|CRYP]]) || 650 MHz<ref name="mission profile"></ref> | ||

|- | |||

| STM32MP15x'''D''' || Basic || 800 MHz<ref name="mission profile"></ref><ref name="frequency">800 MHz part numbers are only available with '1' as junction temperatures range suffix (- 20 to + 105 °C).</ref> | |||

|- | |||

| STM32MP15x'''F''' || Secure boot + Cryptography ([[CRYP internal peripheral|CRYP]]) || 800 MHz<ref name="mission profile"></ref><ref name="frequency"></ref> | |||

|} | |} | ||

=== Packages === | |||

:{| class=" | :{| class="st-table" | ||

| | | STM32MP15xx'''AA''' || TFBGA448 18x18 | ||

|- | |- | ||

| | | STM32MP15xx'''AB''' || LFBGA354 16x16 | ||

|- | |- | ||

| | | STM32MP15xx'''AC''' || TFBGA361 12x12 | ||

|- | |- | ||

| | | STM32MP15xx'''AD''' || TFBGA257 10x10 | ||

|} | |||

=== Junction temperature === | |||

:{| class="st-table" | |||

| STM32MP15xxxx'''1''' || - 20 to + 105 °C<ref name="mission profile"></ref><ref name="frequency"></ref> | |||

|- | |- | ||

| | | STM32MP15xxxx'''3''' || - 40 to + 125 °C<ref name="mission profile"></ref> | ||

|} | |} | ||

== Block | == Block diagram== | ||

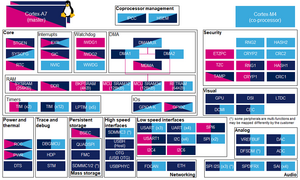

Here below is the | Here below is the STM32MP157F block diagram offering the richest features set of the STM32MP15 microprocessor. | ||

[[File: | [[File: STM32MP157F_marketing_block_diagram.png|center|link=]] | ||

==Technical documentation== | ==Technical documentation== | ||

* [[STM32MP15 resources#Reference manuals|STM32MP15 Reference Manual]]: device and internal peripheral user specifications | * [[STM32MP15 resources#Reference manuals|STM32MP15 Reference Manual]]: device and internal peripheral user specifications | ||

* [[STM32MP15 resources# | * [[STM32MP15 resources#DS12505|STM32MP15 Datasheet]]: electrical characteristics, package and pinout descriptions | ||

==Internal peripherals== | ==Internal peripherals== | ||

| Line 84: | Line 83: | ||

===Supported software distributions=== | ===Supported software distributions=== | ||

{|class=" | {|class="st-table" style="text-align:center; width:95%; cellspacing=0" | ||

|- | |- style="vertical-align:bottom;" | ||

| [[File:ST_logo.png|100px|link=STM32MPU Embedded Software distribution| text |STM32MPU Embedded Software distribution]] <br> [[STM32MPU Embedded Software distribution|'''STM32MPU Embedded Software distribution''']] | |||

| [[File:Android_logo.png|80px|link=:Category:STM32MPU Embedded Software distribution for Android| text |STM32MPU Embedded Software distribution for Android]] <br> [[:Category:STM32MPU Embedded Software distribution for Android|'''STM32MPU Embedded Software distribution for Android''']] | |||

|} | |} | ||

| Line 94: | Line 93: | ||

*Associated release notes | *Associated release notes | ||

==References== | == References and foot notes== | ||

<references/> | <references/> | ||

<noinclude> | |||

{{ReviewsComments|File to be reviewed by the marketing communication team}} | |||

{{PublicationRequestId | 8334 | 2018-08-06 | AnneJ}} | |||

[[Category:STM32 MPU microprocessor devices]] | |||

</noinclude> | |||

Latest revision as of 13:01, 12 February 2020

In a first part, this article shows the STM32MP157 line part number codification and block diagram. STM32MP157 belongs to STM32MP1 Series (refer to the list of part numbers provided below).

The second part of this article digs into technical aspects, and provides entry points to:

- STM32MP15 documentation

- articles dedicated to Internal peripherals that make the transition towards the software frameworks required to control these peripherals

- the list of boards supporting STM32MP15 devices

- the supported software distributions, that can be dowloaded into the STM32MP15 device.

1. Introduction

STM32MP15 microprocessors are based on the Arm® Cortex®-A7 dual core. They support Trustzone mode for secure operations, a Vivante GPU and an Arm® Cortex®-M4 coprocessor.

Arm® Cortex®-M4 coprocessor and its peripheral set are directly inherited from the STM32 MCU family [1].

2. Part number codification

The table below shows the STM32MP15 microprocessor different part numbers available, together with their corresponding internal peripherals, security options and packages.

2.1. STM32MP15x lines

Cortex-A7 Cortex-M4 GPU Display CAN STM32MP151 Single Yes No TFT No STM32MP153 Dual Yes No TFT Yes STM32MP157 Dual Yes Yes TFT/DSI Yes

2.2. Security and Cortex-A7 frequency

2.3. Packages

STM32MP15xxAA TFBGA448 18x18 STM32MP15xxAB LFBGA354 16x16 STM32MP15xxAC TFBGA361 12x12 STM32MP15xxAD TFBGA257 10x10

2.4. Junction temperature

3. Block diagram

Here below is the STM32MP157F block diagram offering the richest features set of the STM32MP15 microprocessor.

4. Technical documentation

- STM32MP15 Reference Manual: device and internal peripheral user specifications

- STM32MP15 Datasheet: electrical characteristics, package and pinout descriptions

5. Internal peripherals

STM32MP15 peripherals overview article gives a description of all the internal peripherals available on STM32MP15 devices, with direct links to the articles where you can find:

- an overview of each peripheral

- the list of instances available for each peripheral type,

- information on the way each instance can be shared between Arm® Cortex®-A7 and Cortex®-M4 cores,

- direct links to the software frameworks used to control the peripheral from different Arm® cores and security modes such as Cortex®-A7 non secure, Cortex®-A7 secure or Cortex®-M4 (non secure).

6. How to get further with STM32MP15 ecosystem

6.1. Boards

The list of boards that integrate STM32MP15 devices can be found in STM32MP15 boards article.

6.2. Supported software distributions

Click the links above to find information on:

- Distribution composition and associated software architecture

- Associated release notes

7. References and foot notes

- ↑ STM32 MCU family

- ↑ Jump up to: 2.0 2.1 2.2 2.3 2.4 2.5 Exposure to maximum rating conditions for extended periods may affect device reliability. Device mission profile (application conditions) is compliant with JEDEC JESD47 qualification standard. Refer to the STM32MP15 Datasheet and AN5438 for further information.

- ↑ Jump up to: 3.0 3.1 3.2 800 MHz part numbers are only available with '1' as junction temperatures range suffix (- 20 to + 105 °C).