Registered User (Created page with "<noinclude> {{ArticleBasedOnModel | Internal peripheral article model}} {{ArticleMainWriter | GeraldB}} {{ArticleApprovedVersion | Jean-ChristopheT | Nobody | No previous...") |

imported>Frq08690 mNo edit summary |

||

| Line 2: | Line 2: | ||

{{ArticleBasedOnModel | [[Internal peripheral article model]]}} | {{ArticleBasedOnModel | [[Internal peripheral article model]]}} | ||

{{ArticleMainWriter | GeraldB}} | {{ArticleMainWriter | GeraldB}} | ||

{{ArticleApprovedVersion | | {{ArticleApprovedVersion | GeraldB | PatrickD (Failed-12Jun'18) | No previous approved version | 10485 - MariaC - 31Jan'19 | 23'May18}} | ||

[[Category:RAM interfaces]] | [[Category:RAM interfaces]] | ||

</noinclude> | </noinclude> | ||

{{ | |||

==Article purpose== | |||

The purpose of this article is to: | |||

* briefly introduce the DDRCTRL and DDRPHYC peripherals and their main features | |||

* indicate the level of security supported by those hardware blocks | |||

* explain how they can be allocated to the three runtime contexts and linked to the corresponding software components | |||

* explain, when necessary, how to configure the DDRCTRL and DDRPHYC peripherals | |||

==Peripheral overview== | |||

'''DDRCTRL''' and '''DDRPHYC''' peripherals are used to configure the physical interface to the external DDR memory.<br /> | |||

===Features=== | |||

Refer to [[STM32MP15 resources#Reference manuals|STM32MP15 reference manuals]] for the complete features list, and to the software components, introduced below, to know which features are really implemented.<br> | |||

===Security support=== | |||

DDRCTRL and DDRPHYC are '''secure aware''' (under [[ETZPC_internal_peripheral|ETZPC]] control).<br /> | |||

The access to the DDR memory can be filtered alone via [[TZC internal peripheral|TZC]] controller: for instance, it is possible to forbid the access from the Cortex<sup>®</sup>-M4 to the DDR region used by the Cortex<sup>®</sup>-A7. | |||

==Peripheral usage and associated software== | |||

===Boot time=== | |||

DDRCTRL and DDRPHYC are kept secure and used by the [[Boot chains overview|FSBL]] to initialize the access to the DDR where it loads the [[U-Boot overview|SSBL (U-Boot)]] for execution.<br /> | |||

STMicroelectronics wants to make the DDR memory configuration as easy as possible, for this reason a '''DDR tuning''' function is available in [[STM32CubeMX]] tool in order to generate the [[Device tree|device tree]] that is given to the [[Boot chains overview|FSBL]] to perform this initialization. | |||

===Runtime=== | |||

====Overview==== | |||

DDRCTRL and DDRPHYC are accessed at runtime by the secure monitor (from the [[Boot chains overview|FSBL]] or [[OP-TEE overview|OP-TEE]]) to put the DDR in self-refresh state before going into Stop or Standby [[Power overview|low power mode]].<br /> | |||

On Standby exit, the [[STM32MP15 ROM code overview|ROM code]] loads the [[Boot chains overview|FSBL]] that configures again the DDRCTRL and DDRPHYC before proceeding with the wake up procedure, till Linux. | |||

<br /> | |||

<br /> | |||

Caution: there is '''no runtime allocation for DDRCTRL and DDRPHYC''' since there are always initialized by the secure context. On the other hand, it is usefull to show that the '''DDR memory itself is only used by the Cortex<sup>®</sup>-A7 non-secure''' for Linux, as shown in the [[STM32MP15_RAM_mapping#Overall_memory_mapping|memory mapping]], so this is the only possible configuration in STMicroelectronics distribution. | |||

====Software frameworks==== | |||

{{:Internal_peripherals_software_table_template}} | |||

| Core/RAM | |||

| [[DDRCTRL and DDRPHYC internal peripherals|DDR via DDRCTRL]] | |||

| | |||

| [[STM32MP15_RAM_mapping#Overall_memory_mapping|Memory mapping]] | |||

| | |||

| | |||

|- | |||

|} | |||

{{ReviewsComments| 12jun'18 PDE: Memory mapping also for secure (OP-TEE in RAM) }} | |||

====Peripheral configuration==== | |||

The configuration is applied during boot time by the SSBL (see [[Boot chains overview]]): [[TF-A_overview|TF-A]] or [[U-Boot overview#SPL: FSBL for basic boot|U-Boot SPL]]. | |||

The configuration by itself (values for DDRCTL and DDRPHY registers) is generated via [[STM32CubeMX]] tool in the device tree for the SSBL according the DDR configuration (type, size, frequency, speed grade). | |||

====Peripheral assignment==== | |||

{{:Internal_peripherals_assignment_table_template}} | |||

<onlyinclude> | |||

| rowspan="1" | Core/RAM | |||

| rowspan="1" | [[DDRCTRL and DDRPHYC internal peripherals|DDR via DDRCTRL]] | |||

| DDR | |||

| | |||

| <span title="system peripheral" style="font-size:21px">✓</span> | |||

| | |||

| | |||

|- | |||

</onlyinclude> | |||

|} | |||

{{ReviewsComments| 12jun'18 PDE: Assigned to NS ??? }} | |||

==How to go further== | |||

Device tree binding of DDR node: | |||

* available in U-boot source : {{CodeSource | U-Boot | doc/device-tree-bindings/ram/st%2Cstm32mp1-ddr.txt | doc/device-tree-bindings/ram/st,stm32mp1-ddr.txt}} | |||

==References== | |||

<references/> | |||

Revision as of 17:10, 31 January 2019

Template:ArticleBasedOnModel Template:ArticleMainWriter Template:ArticleApprovedVersion

1. Article purpose

The purpose of this article is to:

- briefly introduce the DDRCTRL and DDRPHYC peripherals and their main features

- indicate the level of security supported by those hardware blocks

- explain how they can be allocated to the three runtime contexts and linked to the corresponding software components

- explain, when necessary, how to configure the DDRCTRL and DDRPHYC peripherals

2. Peripheral overview

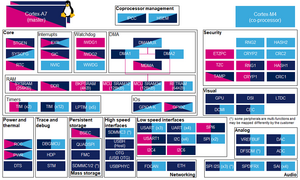

DDRCTRL and DDRPHYC peripherals are used to configure the physical interface to the external DDR memory.

2.1. Features

Refer to STM32MP15 reference manuals for the complete features list, and to the software components, introduced below, to know which features are really implemented.

2.2. Security support

DDRCTRL and DDRPHYC are secure aware (under ETZPC control).

The access to the DDR memory can be filtered alone via TZC controller: for instance, it is possible to forbid the access from the Cortex®-M4 to the DDR region used by the Cortex®-A7.

3. Peripheral usage and associated software

3.1. Boot time

DDRCTRL and DDRPHYC are kept secure and used by the FSBL to initialize the access to the DDR where it loads the SSBL (U-Boot) for execution.

STMicroelectronics wants to make the DDR memory configuration as easy as possible, for this reason a DDR tuning function is available in STM32CubeMX tool in order to generate the device tree that is given to the FSBL to perform this initialization.

3.2. Runtime

3.2.1. Overview

DDRCTRL and DDRPHYC are accessed at runtime by the secure monitor (from the FSBL or OP-TEE) to put the DDR in self-refresh state before going into Stop or Standby low power mode.

On Standby exit, the ROM code loads the FSBL that configures again the DDRCTRL and DDRPHYC before proceeding with the wake up procedure, till Linux.

Caution: there is no runtime allocation for DDRCTRL and DDRPHYC since there are always initialized by the secure context. On the other hand, it is usefull to show that the DDR memory itself is only used by the Cortex®-A7 non-secure for Linux, as shown in the memory mapping, so this is the only possible configuration in STMicroelectronics distribution.

3.2.2. Software frameworks

| Domain | Peripheral | Software frameworks | Comment | ||

|---|---|---|---|---|---|

| Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Core/RAM | DDR via DDRCTRL | Memory mapping | |||

3.2.3. Peripheral configuration

The configuration is applied during boot time by the SSBL (see Boot chains overview): TF-A or U-Boot SPL.

The configuration by itself (values for DDRCTL and DDRPHY registers) is generated via STM32CubeMX tool in the device tree for the SSBL according the DDR configuration (type, size, frequency, speed grade).

3.2.4. Peripheral assignment

Check boxes illustrate the possible peripheral allocations supported by STM32 MPU Embedded Software:

- ☐ means that the peripheral can be assigned (☑) to the given runtime context.

- ✓ is used for system peripherals that cannot be unchecked because they are statically connected in the device.

Refer to How to assign an internal peripheral to a runtime context for more information on how to assign peripherals manually or via STM32CubeMX.

The present chapter describes STMicroelectronics recommendations or choice of implementation. Additional possiblities might be described in STM32MP15 reference manuals.

| Domain | Peripheral | Runtime allocation | Comment | |||

|---|---|---|---|---|---|---|

| Instance | Cortex-A7 secure (OP-TEE) |

Cortex-A7 non-secure (Linux) |

Cortex-M4 (STM32Cube) | |||

| Core/RAM | DDR via DDRCTRL | DDR | ✓ | |||

4. How to go further

Device tree binding of DDR node:

- available in U-boot source : doc/device-tree-bindings/ram/st,stm32mp1-ddr.txt